# 3-phase Brushless Motor Driver IC for Automotive **SPF6102**

## Description

The SPF6102 is 3-phase Brushless Motor Driver IC. The IC is suitable for the applications which the maximum applied voltage to the motor is 150 V or less.

The IC is driven by a bootstrap circuit, and the charge to this boost power supply (boot capacitor) is supplied from the internal auxiliary power supply. This auxiliary power supply is boosted by the internal charge pump circuit and supplies a stable voltage that does not depend on the automotive inherent battery variation to the gate drive circuit.

The IC uses the compact SMD package, HSOP48 with high thermal dissipation and provides high-density mounting. Since the IC has the various protection functions, it can drive 3-phase brushless motor with few external components.

#### **Features**

- AEC-Q100 Qualified

- Built-in Bootstrap Diode

- Built-in Auxiliary Power Supply (VREGx)

- Bare Lead Frame: Pb-free (RoHS compliant)

- Enable Function

- (All phases shutdown with EN = logic low)

- Fault Signal Output at Protect Circuit Activated

- Protections

- Simultaneous On-state Prevention

- VBB Pin Overvoltage Protection (VBB\_OVP): Autorestart

- Undervoltage Lockout

VBB Pin (VBB\_UVLO): Auto-restart

VDD Pin (VDD\_UVLO): Auto-restart

VREGx Pin (VREGx\_UVLO): Auto-restart

- Thermal Shutdown (TSD)

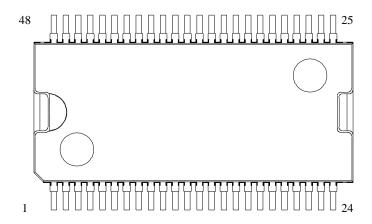

### **Package**

HSOP48

Not to scale

### **Specifications**

- Maximum Main Supply Voltage:  $V_{DC} = 150 \text{ V}$

- Maximum Logic Supply Voltage: VBB = 35 V

- Typical On-resistance of Internal Drive Circuit Sink:  $4 \Omega$  Source:  $5 \Omega$

## **Applications**

For driving DC brushless motor such as:

- Inverter

- Onboard Charger (OBC)

- Battery Management System (BMS)

## **Contents**

| Descriptio | n                                             | 1  |

|------------|-----------------------------------------------|----|

| Contents - |                                               | 2  |

| 1. Absolu  | te Maximum Ratings                            | 3  |

| 2. Recom   | mended Operating Conditions                   | 3  |

|            | cal Characteristics                           |    |

|            | Diagram                                       |    |

|            | nfiguration Definitions                       |    |

|            | l Application                                 |    |

|            |                                               |    |

|            | Гable                                         |    |

| 8. Physic  | al Dimensions                                 | 10 |

| 9. Marki   | ng Diagram                                    | 11 |

| 10. Operat | ional Descriptions                            | 12 |

| 10.1. Pi   | n Descriptions                                | 12 |

| 10.1.1     | . VBB                                         | 12 |

| 10.1.2     | . VDD                                         | 12 |

| 10.1.3     | . VREGx                                       | 12 |

| 10.1.4     | . CP1x and CP2x                               | 12 |

| 10.1.5     | . Cx 12                                       |    |

| 10.1.6     | . HIx and LOx                                 | 12 |

| 10.1.7     | . EN12                                        |    |

| 10.1.8     | . FLT                                         | 12 |

| 10.1.9     | . GHx and GLx                                 | 12 |

|            | 0. Sx and SLx                                 |    |

| 10.1.1     | 1. LGND and PGND                              | 13 |

|            | asic Operation                                |    |

| 10.3. Si   | multaneous On-state Prevention                | 13 |

|            | otections                                     |    |

|            | . VBB Pin Overvoltage Protection (VBB_OVP)    |    |

| 10.4.2     | . VBB Pin Undervoltage Lockout (VBB_UVLO)     | 14 |

| 10.4.3     | . VDD Pin Undervoltage Lockout (VDD_UVLO)     | 14 |

| 10.4.4     | . VREGx Pin Undervoltage Lockout (VREGx_UVLO) | 14 |

|            | . Thermal Shutdown (TSD)                      |    |

|            | nable Function                                |    |

|            | Notes                                         |    |

## 1. Absolute Maximum Ratings

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); and current coming out of the IC (sourcing) is negative current (-).

Unless specifically noted,  $T_A = 25$  °C, and reference ground is the LGND pin.

| Parameter                                 | Symbol                | Conditions         | Ratings     | Unit |

|-------------------------------------------|-----------------------|--------------------|-------------|------|

| Division Comment Visites                  | $V_{BB1}$             |                    | -0.6 to 35  | V    |

| Direct Current Input Voltage              | $V_{BB2}$             | T < 400 ms         | 40          | V    |

| VREGx Pin Voltage                         | $V_{\text{REG}}$      |                    | -0.6 to 18  | V    |

| VDD Pin Voltage                           | $V_{\mathrm{DD}}$     |                    | -0.3 to 6   | V    |

| HIx, LOx and EN Pin Voltage               | $V_{\rm IN}$          |                    | -0.3 to 6   | V    |

| LSx Pin Voltage                           | $V_{LSx}$             |                    | -4 to 4     | V    |

| GLx Pin Voltage                           | $V_{GLx}$             |                    | -4 to 18    | V    |

| Sx Pin Voltage                            | $V_{Sx}$              |                    | -4 to 132   | V    |

| GHx Pin Voltage                           | $V_{GHx}$             |                    | -4 to 150   | V    |

| Cx Pin Voltage                            | $V_{Cx}$              |                    | -0.3 to 150 | V    |

| FLT Pin Voltage                           | $V_{\mathrm{FLT}}$    |                    | -0.3 to 6   | V    |

| CP1x Pin Voltage                          | V <sub>CP1x</sub>     |                    | -0.3 to 18  | V    |

| CP2x Pin Voltage                          | $V_{\text{CP2x}}$     |                    | -0.3 to 18  | V    |

| D. Distinction                            | $P_{D1}$              | Infinite Heatsink  | 30.4        | W    |

| Power Dissipation                         | $P_{D2}$              | Glass-epoxy Board* | 3.57        | W    |

| Junction Temperature                      | $T_{J}$               |                    | -40 to 150  | °C   |

| Operating Ambient Temperature             | $T_{OP}$              |                    | -40 to 105  | °C   |

| Storage Temperature                       | $T_{STG}$             |                    | -40 to 150  | °C   |

| Junction-to-Case Thermal Resistance       | $\theta_{	ext{J-C}}$  |                    | 4.1         | °C/W |

| Junction-to-Ambient Thermal<br>Resistance | $\theta_{\text{J-A}}$ |                    | 35          | °C/W |

<sup>\*</sup> Board size is 50 mm  $\times$  74 mm, thickness of glass-epoxy is 1.6 mm, and thickness of copper laminate is 18  $\mu$ m.

## 2. Recommended Operating Conditions

| Parameter                    | Symbol      | Conditions | Min. | Тур. | Max. | Unit |

|------------------------------|-------------|------------|------|------|------|------|

| VBB Pin Input Supply Voltage | $V_{BB}$    |            | 7    | 14   | 18   | V    |

| VDD Pin Input Supply Voltage | $V_{ m DD}$ |            | 4.5  | 5.0  | 5.5  | V    |

#### **3. Electrical Characteristics**

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); and current

coming out of the IC (sourcing) is negative current (–). Unless specifically noted,  $T_A = -30$  °C to 125 °C,  $V_{BB} = 14$  V,  $V_{DD} = EN = 5$  V,  $C_{REGx} = 10$   $\mu F$ ,  $f_{PWM} = 22.5$  kHz, and  $C_{Px} = C_{Bx} = 0.1 \mu F$ .

| Parameter                         | Symbol                  | Conditions                                                   | Min. | Тур. | Max. | Unit |

|-----------------------------------|-------------------------|--------------------------------------------------------------|------|------|------|------|

| VBB Input Current 1               | I <sub>BB1</sub>        | VDD = EN = 0 V                                               |      | 5    |      | mA   |

|                                   |                         | HIx = LOx = 5 V                                              |      |      |      |      |

| VBB Input Current 2               | I <sub>BB2</sub>        | HIx = LOx = 5 V                                              |      | 15   |      | mA   |

| VDD Input Current                 | $I_{DD}$                | HIx = LOx = 5 V                                              |      | 1.0  | 5.0  | mA   |

| Cx Pin, GHx Pin, Sx Pin Current   | $I_{CxL}$               | Cx = GHx = Sx = 90  V                                        |      |      | 100  | μA   |

| VREGx Output Voltage 1            | V <sub>REGx1</sub>      | 7 V < VBB < 8 V                                              | 10   | 12   | 15   | V    |

| VREGx Output Voltage 2            | $V_{REGx2}$             | 8 V ≤ VBB                                                    | 12   | 15   | 18   | V    |

| Enable Voltage                    | $V_{\text{ENH}}$        | III 5 V                                                      | 2.0  |      | _    | V    |

| Enable Release Voltage            | $V_{\text{ENL}}$        | HIx = 5 V,<br>LSx = Sx = LGND                                | _    |      | 0.8  | V    |

| Enable Voltage Hysteresis         | $\Delta V_{EN}$         |                                                              | —    | 0.15 | —    | V    |

| HIx Pin Logic Low Input Voltage   | $V_{HIxH}$              |                                                              |      | _    | 0.8  | V    |

| HIx Pin Logic High Input Voltage  | $V_{HIxL}$              | HIx = 5 V,<br>LSx = Sx = LGND                                | 2.0  | _    | _    | V    |

| HIx Pin Input Voltage Hysteresis  | $\Delta V_{HIx}$        | ESX = SX = EST(E                                             | _    | 0.15 | _    | V    |

| LOx Pin Logic Low Input Voltage   | $V_{LOxH}$              |                                                              | _    | _    | 0.8  | V    |

| LOx Pin Logic High Input Voltage  | $V_{LOxL}$              | LOx = 5 V,<br>LSx = Sx = LGND                                | 2.0  | _    | —    | V    |

| LOx Pin Input Voltage Hysteresis  | $\Delta V_{LOx}$        | LDX = DX = LOND                                              |      | 0.15 | _    | V    |

| EN Pin Input Current (H)          | $I_{ENH}$               | EN = 5 V                                                     | _    | 100  | 500  | μΑ   |

| EN Pin Input Current (L)          | $I_{ENL}$               | EN = 0 V                                                     | -100 |      |      | μΑ   |

| HIx Pin Input Current (H)         | $I_{HIxH}$              | HIx = 0 V                                                    | -500 | -100 | _    | μΑ   |

| HIx Pin Input Current (L)         | $I_{HIxL}$              | HIx = 5 V                                                    | _    | _    | 100  | μΑ   |

| LOx Pin Input Current (H)         | $I_{LOxH}$              | LOx = 0 V                                                    | -500 | -100 | _    | μΑ   |

| LOx Pin Input Current (L)         | $I_{LOxL}$              | LOx = 5 V                                                    | _    |      | 100  | μΑ   |

| FLT Pin Output Saturation Voltage | $V_{FLT}$               | $I_{FLT(L)} = 1 \text{ mA}$                                  | _    |      | 0.4  | V    |

| Bootstrap Diode Forward Voltage   | V <sub>TH(BD)</sub>     | $I_F = 1 \text{ mA}$                                         | 0.4  | 1.2  | 1.7  | V    |

| GHx Pin Source On-resistance      | R <sub>DS(SC_GHx)</sub> | HIx = 0 V,                                                   | 3    | 5.0  | 10   | Ω    |

| GHx Pin Sink On-resistance        | R <sub>DS(SI_GHx)</sub> | LOx = 5 V,<br>LSx = Sx = LGND,<br>Cx > 10 V,<br>VREGx > 10 V | 2    | 4.0  | 8    | Ω    |

| GLx Pin Source On-resistance      | R <sub>DS(SC_GLx)</sub> | HIx = 5 V,                                                   | 3    | 5.0  | 10   | Ω    |

| GLx Pin Sink On-resistance        | R <sub>DS(SI_GLx)</sub> | LOx = 0 V, $LSx = Sx = LGND,$ $Cx > 10 V,$ $VREGx > 10 V$    | 2    | 4.0  | 8    | Ω    |

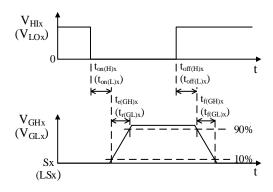

| High side Output Delay Time       | t <sub>on(H)x</sub>     | Ciss = 3300 pF,                                              |      | 250  | _    | ns   |

| High-side Output Delay Time       | $t_{\rm off(H)x}$       | see Figure 3-1                                               |      | 200  | _    | ns   |

| Low side Output Deley Time        | t <sub>on(L)x</sub>     | Ciss = 3300 pF,                                              |      | 250  | _    | ns   |

| Low-side Output Delay Time        | t <sub>off(L)x</sub>    | see Figure 3-1                                               |      | 200  | _    | ns   |

### **SPF6102**

| Parameter                                            | Symbol                     | Conditions                                                                              | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| GHx Pin Output Rise Time <sup>(1)</sup>              | t <sub>r(GHx)</sub>        | 20% V <sub>GHx</sub> to 80% V <sub>GHx</sub> ,                                          | 10   |      | 100  | ns   |

| GHx Pin Output Fall Time(1)                          | $t_{f(GHx)}$               | Ciss = 3300 pF,<br>see Figure 3-1                                                       | 10   | _    | 100  | ns   |

| GLx Pin Output Rise Time <sup>(1)</sup>              | $t_{r(GLx)}$               | $\begin{array}{c} 20\%  V_{GLx} \ to \ 80\%  V_{GLx}, \\ Ciss = 3300 \ pF, \end{array}$ | 10   |      | 100  | ns   |

| GLx Pin Output Fall Time <sup>(1)</sup>              | $t_{f(GLx)}$               | see Figure 3-1                                                                          | 10   |      | 100  | ns   |

| VDD Pin Undervoltage Lockout Release<br>Voltage      | $V_{\text{UVDD(H)}}$       |                                                                                         | _    | 4.0  |      | V    |

| VDD Pin Undervoltage Lockout<br>Operating Voltage    | $V_{\text{UVDD(L)}}$       |                                                                                         | _    | 3.8  |      | V    |

| VDD Pin Undervoltage Lockout<br>Hysteresis           | $\Delta V_{\mathrm{UVDD}}$ |                                                                                         | _    | 0.2  |      | V    |

| VBB Pin Overvoltage Protection<br>Operating Voltage  | V <sub>OVBB(H)</sub>       |                                                                                         | _    | 28   | _    | V    |

| VBB Pin Overvoltage Protection<br>Release Voltage    | V <sub>OVBB(L)</sub>       |                                                                                         | _    | 25   | _    | V    |

| VBB Pin Overvoltage Protection Hysteresis            | $\Delta V_{OVBB}$          |                                                                                         | _    | 3    | _    | V    |

| VBB Pin Undervoltage Lockout Release<br>Voltage      | $V_{\text{UVBB(H)}}$       |                                                                                         | 6.0  | 6.5  | 7.0  | V    |

| VBB Pin Undervoltage Lockout<br>Operating Voltage    | V <sub>UVBB(L)</sub>       |                                                                                         | 5.5  | 6.1  | 6.6  | V    |

| VBB Pin Undervoltage Lockout<br>Hysteresis           | $\Delta V_{UVBB}$          |                                                                                         | _    | 0.4  | _    | V    |

| VREGx Pin Undervoltage Lockout<br>Release Voltage    | V <sub>UVREGx(H)</sub>     |                                                                                         | 6.5  | 7.5  | 8.5  | V    |

| VREGx Pin Undervoltage Lockout<br>Operating Voltage  | $V_{\text{UVREGx}(L)}$     |                                                                                         | 6.0  | 7.1  | 8.2  | V    |

| VREGx Pin Undervoltage Lockout<br>Hysteresis         | $\Delta V_{UVREGx}$        |                                                                                         | _    | 0.4  | _    | V    |

| Thermal Shutdown Starting Temperature <sup>(2)</sup> | $T_{TSD}$                  |                                                                                         | 151  | _    | _    | °C   |

Figure 3-1. Definition of Switching Time

SPF6102-DSE Rev.1.3 Aug. 02, 2022

$<sup>^{(1)}</sup>$  When the outputs of the GHx and GLx pins are turned on/ off, the typical design values of output pulse current of the GHx and GLx pins are as follows (conditions: VREGx = 15 V, t < 100 ns, and  $T_A$  = 25 °C):

<sup>•</sup> Turning on:  $I_{SOURCE} = 2.0 \text{ A}$

<sup>•</sup> Turning off:  $I_{SINK} = 2.3 A$

$<sup>^{(2)}</sup>$  It is guaranteed by design. The typical design value of thermal shutdown starting temperature is 165  $^{\circ}$ C.

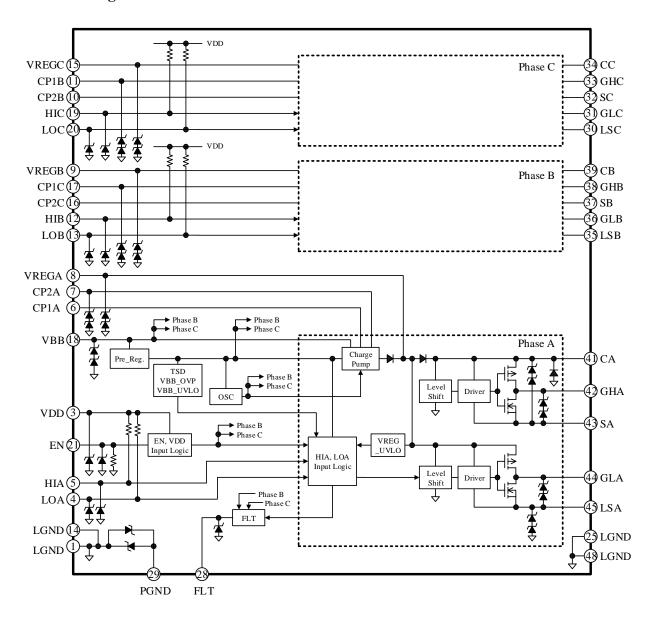

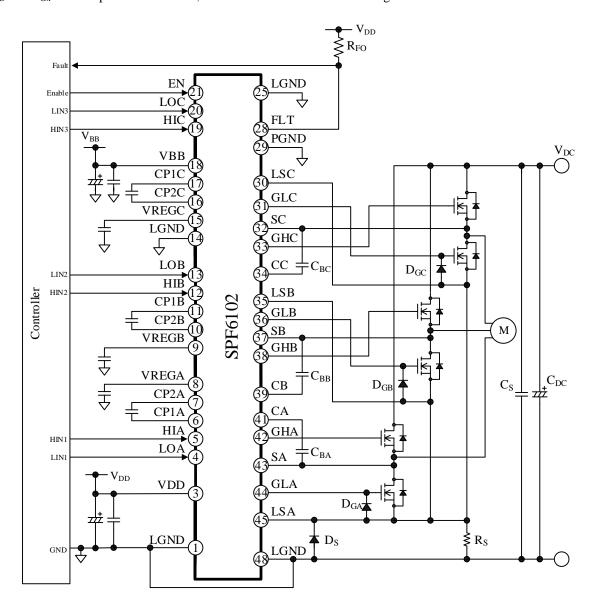

## 4. Block Diagram

#### **Pin Configuration Definitions 5.**

| Pin<br>Number | Pin<br>Name | Function                                                           | Pin<br>Number | Pin<br>Name | Function                                   |

|---------------|-------------|--------------------------------------------------------------------|---------------|-------------|--------------------------------------------|

| 1             | LGND        | Control ground                                                     | 25            | LGND        | Control ground                             |

| 2             | (NC)        | (No connection)                                                    | 26            | (NC)        | (No connection)                            |

| 3             | VDD         | Logic supply input for input signal                                | 27            | (NC)        | (No connection)                            |

| 4             | LOA         | Low-side logic input for A-phase                                   | 28            | FLT         | Fault signal output (Open drain)           |

| 5             | HIA         | High-side logic input for A-phase                                  | 29            | PGND        | Power ground                               |

| 6             | CP1A        | Capacitor connect pin 1 for A-phase charge pump circuit            | 30            | LSC         | C-phase low-side source connection         |

| 7             | CP2A        | Capacitor connect pin 2 for A-phase charge pump circuit            | 31            | GLC         | C-phase low-side gate drive signal output  |

| 8             | VREGA       | Capacitor connect pin for A-phase high-<br>and low-side gate drive | 32            | SC          | C-phase high-side source connection        |

| 9             | VREGB       | Capacitor connect pin for B-phase high-<br>and low-side gate drive | 33            | GHC         | C-phase high-side gate drive signal output |

| 10            | CP2B        | Capacitor connect pin 2 for B-phase charge pump circuit            | 34            | CC          | C-phase boot capacitor connection          |

| 11            | CP1B        | Capacitor connect pin 1 for B-phase charge pump circuit            | 35            | LSB         | B-phase low-side source connection         |

| 12            | HIB         | High-side logic input for B-phase                                  | 36            | GLB         | B-phase low-side gate drive signal output  |

| 13            | LOB         | Low side logic input for B-phase                                   | 37            | SB          | B-phase high-side source connection        |

| 14            | LGND        | Control ground                                                     | 38            | GHB         | B-phase high-side gate drive signal output |

| 15            | VREGC       | Capacitor connect pin for C-phase high-<br>and low-side gate drive | 39            | СВ          | B-phase boot capacitor connection          |

| 16            | CP2C        | Capacitor connect pin 2 for C-phase charge pump circuit            | 40            | (NC)        | (No connection)                            |

| 17            | CP1C        | Capacitor connect pin 1 for C-phase charge pump circuit            | 41            | CA          | A-phase boot capacitor connection          |

| 18            | VBB         | Main supply input                                                  | 42            | GHA         | A-phase high-side gate drive signal output |

| 19            | HIC         | High side logic input for C-phase                                  | 43            | SA          | A-phase high-side source connection        |

| 20            | LOC         | Low side Logic input for C-phase                                   | 44            | GLA         | A-phase low-side gate drive signal output  |

| 21            | EN          | Enable signal input                                                | 45            | LSA         | A-phase low-side source connection         |

| 22            | (NC)        | (No connection)                                                    | 46            | (NC)        | (No connection)                            |

| 23            | (NC)        | (No connection)                                                    | 47            | (NC)        | (No connection)                            |

| 24            | (NC)        | (No connection)                                                    | 48            | LGND        | Control ground                             |

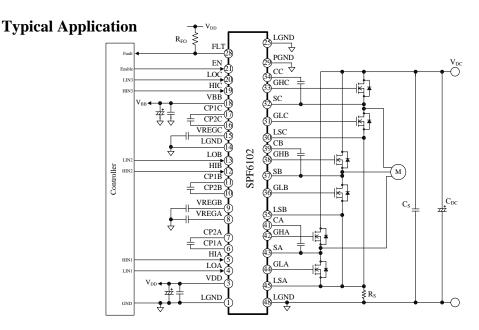

## 6. Typical Application

In the case of the application so that the LSx pin voltage exceeds the absolute maximum rating of  $\pm 4$  V, a diode, D<sub>S</sub>, must be added between the LSx pin and the LGND pin.

If the GLx pin voltage becomes lower by about 0.6 V to 1.8 V than the LSx pin voltage, the IC may be damaged. To avoid the situation, a diode,  $D_{GX}$ , must be added between the GLx pin and the LSx pin.

D<sub>S</sub> and D<sub>Gx</sub> must be placed near the IC, and connected with a minimal length of traces.

Figure 6-1. Typical Application

## 7. Truth Table

Table 7-1. Truth Table for Operation Modes

| M. 1.                           | Inpu | t Pin | Output Pin |     |      | Remarks                             |  |

|---------------------------------|------|-------|------------|-----|------|-------------------------------------|--|

| Mode                            | HIx  | LOx   | GHx        | GLx | FLT* | Remarks                             |  |

|                                 | Н    | Н     | L          | L   | Н    |                                     |  |

|                                 | L    | Н     | Н          | L   | Н    |                                     |  |

| Normal Operation                | Н    | L     | L          | Н   | Н    |                                     |  |

|                                 | L    | L     | L          | L   | Н    | Simultaneous<br>On-state Prevention |  |

|                                 | Н    | Н     | L          | L   | L    |                                     |  |

| VBB Pin                         | L    | Н     | L          | L   | L    |                                     |  |

| Undervoltage Lockout (VBB_UVLO) | Н    | L     | L          | L   | L    |                                     |  |

| (\forall BB_0 \forall B0)       | L    | L     | L          | L   | L    |                                     |  |

|                                 | Н    | Н     | L          | L   | L    |                                     |  |

| VDD Pin                         | L    | Н     | L          | L   | L    |                                     |  |

| Undervoltage Lockout (VDD_UVLO) | Н    | L     | L          | L   | L    |                                     |  |

| (122_8 126)                     | L    | L     | L          | L   | L    |                                     |  |

|                                 | Н    | Н     | L          | L   | Н    |                                     |  |

| Enable Signal Input             | L    | Н     | L          | L   | Н    |                                     |  |

| (EN pin is low level)           | Н    | L     | L          | L   | Н    |                                     |  |

|                                 | L    | L     | L          | L   | Н    |                                     |  |

|                                 | Н    | Н     | L          | L   | L    |                                     |  |

| VREGx Pin                       | L    | Н     | Н          | L   | L    |                                     |  |

| Undervoltage Lockout            | Н    | L     | L          | Н   | L    |                                     |  |

| (VREGx_UVLO)                    | L    | L     | L          | L   | L    | Simultaneous<br>On-state Prevention |  |

|                                 | Н    | Н     | L          | L   | L    |                                     |  |

| Thermal Shutdown (TSD)          | L    | Н     | L          | L   | L    |                                     |  |

| Thermal Shutdown (13D)          | Н    | L     | L          | L   | L    |                                     |  |

|                                 | L    | L     | L          | L   | L    |                                     |  |

<sup>\*</sup>The FLT pin is pulled up to the VDD pin.

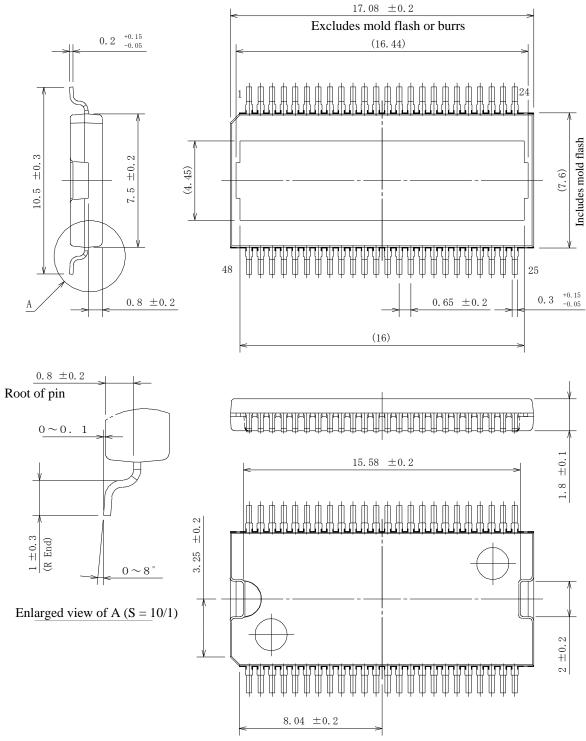

#### 8. **Physical Dimensions**

### • HSOP48 Package

## **NOTES:**

- Dimensions in millimeters

- Bare lead frame: Pb-free (RoHS compliant)

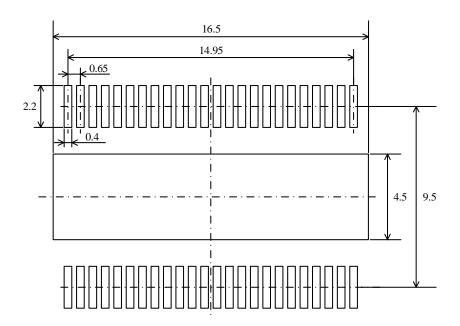

### • HSOP48 Land Pattern Example

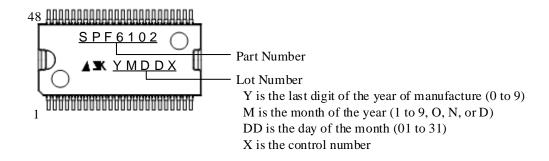

#### 9. **Marking Diagram**

### 10. Operational Descriptions

All the characteristic values given in this section are typical values, unless they are specified as minimum or maximum. Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); and current coming out of the IC (sourcing) is negative current (-).

For pin descriptions, this section employs a notation system that denotes a pin name or an electronic symbol name with the arbitrary letter "x", depending on context. The A, B, and C phases of 3-phase motor are represented as the alphabets A, B, and C, respectively. Thus, "(the) HIx pin" is used when referring to either or all of the HIA, HIB, or HIC pin.

#### 10.1. Pin Descriptions

#### 10.1.1. VBB

This is the main supply input pin of the IC. Recommended applied voltage to the VBB pin is 7 V to 18 V.

When the same power supply is connected to the VBB pin and the external output transistors, power supply loop trace should be designed as wide and short as possible. A Bypass capacitor for noise reduction should be connected to the VBB pin as needed. The bypass capacitor should be placed near the VBB pin, and connected to the VBB pin with a minimal length of traces.

#### 10.1.2. VDD

This is the supply input for input logic circuit. Recommended applied voltage to the VDD pin is 4.5 V to 5.5 V.

## 10.1.3. VREGx

The power supply of high- and low-side gate drive circuit is generated by the internal charge pump circuit. Thus, the gate can be driven stably even if the VBB pin voltage is low (7 V or more).

Capacitor (10  $\mu F$  or more is recommended) for holding supply voltage of gate drive circuit should be connected to the VREGx pin. External power supply connection is unnecessary.

#### 10.1.4. CP1x and CP2x

Connect a capacitor for internal charge pump circuit between the CP1x pin and the CP2x pin. The recommended capacitance is 0.1  $\mu F.$

#### 10.1.5. Cx

Connect a high-side boot capacitor,  $C_{Bx}$ , between the Cx pin and the Sx pin. The recommended capacitance of  $C_{Bx}$  is  $0.1~\mu F$  or more. Since the capacitance depends on the drive frequency and control duty, the setting is required according to the application. For proper startup, turn on the low-side output transistors first, and then charge  $C_{Bx}$  up to its maximum capacity.

#### **10.1.6. HIx and LOx**

These are the signal input pins. The HIx pin acts as high-side controller whereas the LOx pin acts as low-side controller. Since the HIx and LOx pins incorporate a pull-up resistor, the initial state is high (see the block diagram in Section 4).

The width of the input signals to the HIx and LOx pins is required 500 ns or more.

Note that dead time setting for the input signals of the HIx and LOx pins must be done because the IC does not have a dead time generator. Dead time must be set so that the simultaneous on-state does not occur according to the output transistors to be used.

#### 10.1.7. EN

When the high signal is input to the EN pin, all output signals of the GHx and GLx pins become logic low. Since the EN pin incorporates a pull-down resistor, the initial state is low (see the block diagram in Section 4).

#### 10.1.8. FLT

This is the output pin of fault signal. Pull up the FLT pin because the FLT pin is open drain. When the FLT pin is pulled up to the power supply of 5 V, the recommended pull-up resistor is about 20 k $\Omega$ . The FLT pin logic level is high in normal operation, and becomes low when one or more the following protections are activated.

- VBB pin Overvoltage Protection (VBB\_OVP)

- VBB pin Undervoltage Lockout (VBB\_UVLO)

- VDD pin Undervoltage Lockout (VDD\_UVLO)

- VREGx pin Undervoltage Lockout (VREGx\_UVLO)

- Thermal Shutdown (TSD)

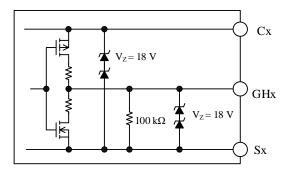

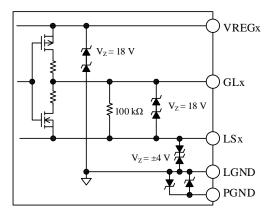

#### 10.1.9. GHx and GLx

These are the gate drive outputs, and are connected to the gate of external output transistors. The GHx pin acts as high-side controller whereas the GLx pin acts as low-side controller. A pull-down resistor of 100 k $\Omega$  (typ.) and protection Zener diodes (the Zener diode) of 18 V (typ.) are internally connected between the GHx pin and

the Sx pin, and between the GLx pin and the LSx pin respectively (see Figure 10-1 and Figure 10-2).

When the current from motor flows to the forward direction of this Zener diode, this may be damaged. In the application that the current flows to the forward direction of the Zener diode, an external diode,  $D_{Gx}$ , must be added between the GHx pin and the Sx pin, and between the GLx pin and the LSx pin respectively (see Figure 6-1).

Figure 10-1. Internal Circuit of High-side Output

Figure 10-2. Internal Circuit of Low-side Output

#### 10.1.10. Sx and SLx

Connect the Sx pin to the source pin of high-side output transistors and the drain pin of low-side output transistors, and the LSx pin to the source pin of low-side output transistors.

An ESD protection bidirectional Zener diode of  $\pm 4$  V is internally connected between the LSx pin and the LGND pin (see Figure 10-2). In the application that the voltage of  $\pm 4$  V or more is applied between the Sx pin and the LGND pin, the external diode,  $D_S$ , must be connected between the LSx pin and the LGND pin (see Figure 6-1).

#### 10.1.11. LGND and PGND

The LGND pin is control ground of the IC. The PGND pin is power ground. A Zener diode is internally connected bidirectionally between the LGND pin and the PGND pin in parallel (see Figure 10-2).

#### 10.2. Basic Operation

At startup, the voltage is applied to the VBB and VDD pins which are the power supply of the IC. Then, the high signal is input to the EN pin. After that, input the signal to the HIx and LOx pins; and on/off controls of the output transistors start.

When the low signal is input to the HIx pin, high-side gate output (the GHx pin) becomes logic high. When the low signal is input to the LO pin, low-side gate output (the GLx pin) becomes logic high (see Table 7-1).

The EN pin has an internally low-pass filter of 2.5  $\mu$ s for the noise malfunction prevention. The HIx and LOx pins do not have internal low-pass filter.

#### 10.3. Simultaneous On-state Prevention

When the low signal is input to the HIx and LOx pins at once, the Simultaneous On-state Prevention is activated, and the outputs of the GHx and GLx pins become logic low. This prevents the breakdown of the output transistors.

#### 10.4. Protections

The IC has the following protection functions.

When the following protections are activated, the outputs of the GHx and GLx pins become logic low, and stop the output transistors. In addition, the fault signal is output (the FLT pin logic level becomes low).

When the protection is released after the fault conditions are removed, the FLT output becomes logic high. Then, the GHx and GLx pins restart output the signals according to the input commands on the HIx and LOx pins from the next falling edge.

However, during VREGx\_UVLO is activated, the IC outputs the fault signal with maintaining the outputs of the GHx and GLx pins according to input signal.

- VBB Pin Overvoltage Protection (VBB\_OVP)

- VBB Pin Undervoltage Lockout (VBB\_UVLO)

- VDD Pin Undervoltage Lockout (VDD UVLO)

- VREGx Pin Undervoltage Lockout (VREGx\_UVLO)

- Thermal Shutdown (TSD)

# 10.4.1. VBB Pin Overvoltage Protection (VBB OVP)

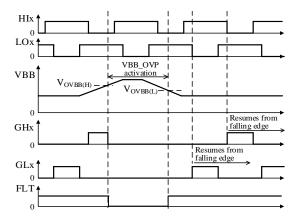

When the VBB pin voltage increases to the VBB pin overvoltage protection operating voltage  $V_{\text{OVBB(H)}} = 28$  V or more, VBB\_OVP is activated. When the VBB pin voltage decreases to the release voltage  $V_{\text{OVBB(L)}} = 25$  V or less, the IC returns to the normal operation.

Figure 10-3. Operational Waveform of VBB\_OVP

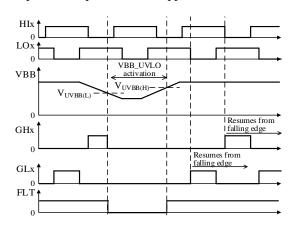

# 10.4.2. VBB Pin Undervoltage Lockout (VBB UVLO)

The VBB pin voltage decrease to the VBB pin undervoltage lockout operating voltage  $V_{\text{UVBB(L)}} = 6.1 \text{ V}$  or less, VBB\_UVLO is activated. When the VBB pin voltage increases to the release voltage  $V_{\text{UVBB(H)}} = 6.5 \text{ V}$  or more, the IC returns to the normal operation. During the VBB\_UVLO activation, the internal charge pump circuit (OSC circuit operation is maintained) and the VREG pin boost operation are stopped.

Figure 10-4. Operational Waveform of VBB\_UVLO

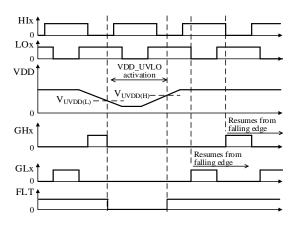

# 10.4.3. VDD Pin Undervoltage Lockout (VDD UVLO)

When the VDD pin voltage decreases to the VDD pin undervoltage lockout operating voltage  $V_{UVDD(L)}$ = 3.8 V or less, the VDD\_UVLO is activated.

When the VDD pin voltage increases to the release voltage  $V_{\rm UVDD(H)}\!=\!4.0~V$  or more, the IC returns to the normal operation.

Figure 10-5. Operational Waveform of VDD\_UVLO

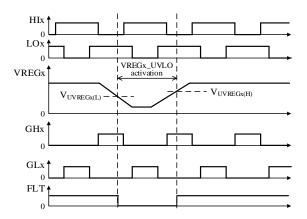

# 10.4.4. VREGx Pin Undervoltage Lockout (VREGx\_UVLO)

When the VREGx pin voltage decreases to VREGx pin undervoltage lockout operating voltage  $V_{UVREGx(L)} = 7.1~V$  or less due to the leak current of the capacitor connecting to the VREG pin, the VREGx\_UVLO is activated.

When the VREG pin voltage increases to the release voltage  $V_{\rm UVREGx(H)} = 7.5~V$  or more, the IC returns to the normal operation.

Figure 10-6. Operational Waveform of VREGx\_UVLO

### 10.4.5. Thermal Shutdown (TSD)

When the junction temperature of the IC increases to  $T_{TSD} = 151~^{\circ}C$  (min.) or more, the TSD is activated. The design value of TSD operating temperature is 165  $^{\circ}C$  (typ.). TSD has the temperature hysteresis. When the temperature decreases by about 10  $^{\circ}C$  from the junction temperature of TSD operation, TSD is released, and the IC returns to the normal operation.

TSD protects the IC against instantaneous heat generation, and does not guarantee the operation including reliability for a state that the heat generation continues for a long time.

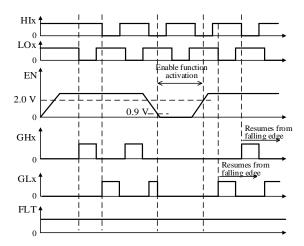

#### 10.5. Enable Function

The IC has an enable function.

When the low signal (0.8 V or less) is input to the EN pin, the input signals of the GHx and GLx pins become logic low. When the high signal (2.0 V or more) is input to the EN pin, the GHx and GLx pins restart output the signals according to the input commands on the HIx and LOx pins from the next falling edge. During the EN pin logic is low, the FLT pin logic level is maintained high.

Figure 10-7 Operational Waveform of Enable Function

#### **Important Notes**

- All data, illustrations, graphs, tables and any other information included in this document (the "Information") as to Sanken's products listed herein (the "Sanken Products") are current as of the date this document is issued. The Information is subject to any change without notice due to improvement of the Sanken Products, etc. Please make sure to confirm with a Sanken sales representative that the contents set forth in this document reflect the latest revisions before use.

- The Sanken Products are intended for use as components of electronic equipment or apparatus (transportation equipment and its control systems, home appliances, office equipment, telecommunication equipment, measuring equipment, etc.). Prior to use of the Sanken Products, please put your signature, or affix your name and seal, on the specification documents of the Sanken Products and return them to Sanken. If considering use of the Sanken Products for any applications that require higher reliability (traffic signal control systems or equipment, disaster/crime alarm systems, etc.), you must contact a Sanken sales representative to discuss the suitability of such use and put your signature, or affix your name and seal, on the specification documents of the Sanken Products and return them to Sanken, prior to the use of the Sanken Products. The Sanken Products are not intended for use in any applications that require extremely high reliability such as: aerospace equipment; nuclear power control systems; and medical equipment or systems, whose failure or malfunction may result in death or serious injury to people, i.e., medical devices in Class III or a higher class as defined by relevant laws of Japan (collectively, the "Specific Applications"). Sanken assumes no liability or responsibility whatsoever for any and all damages and losses that may be suffered by you, users or any third party, resulting from the use of the Sanken Products in the Specific Applications or in manner not in compliance with the instructions set forth herein.

- In the event of using the Sanken Products by either (i) combining other products or materials or both therewith or (ii) physically, chemically or otherwise processing or treating or both the same, you must duly consider all possible risks that may result from all such uses in advance and proceed therewith at your own responsibility.

- Although Sanken is making efforts to enhance the quality and reliability of its products, it is impossible to completely avoid the occurrence of any failure or defect or both in semiconductor products at a certain rate. You must take, at your own responsibility, preventative measures including using a sufficient safety design and confirming safety of any equipment or systems in/for which the Sanken Products are used, upon due consideration of a failure occurrence rate and derating, etc., in order not to cause any human injury or death, fire accident or social harm which may result from any failure or malfunction of the Sanken Products. Please refer to the relevant specification documents and Sanken's official website in relation to derating.

- No anti-radioactive ray design has been adopted for the Sanken Products.

- The circuit constant, operation examples, circuit examples, pattern layout examples, design examples, recommended examples, all information and evaluation results based thereon, etc., described in this document are presented for the sole purpose of reference of use of the Sanken Products.

- Sanken assumes no responsibility whatsoever for any and all damages and losses that may be suffered by you, users or any third party, or any possible infringement of any and all property rights including intellectual property rights and any other rights of you, users or any third party, resulting from the Information.

- No information in this document can be transcribed or copied or both without Sanken's prior written consent.

- Regarding the Information, no license, express, implied or otherwise, is granted hereby under any intellectual property rights and any other rights of Sanken.

- Unless otherwise agreed in writing between Sanken and you, Sanken makes no warranty of any kind, whether express or implied, including, without limitation, any warranty (i) as to the quality or performance of the Sanken Products (such as implied warranty of merchantability, and implied warranty of fitness for a particular purpose or special environment), (ii) that any Sanken Product is delivered free of claims of third parties by way of infringement or the like, (iii) that may arise from course of performance, course of dealing or usage of trade, and (iv) as to the Information (including its accuracy, usefulness, and reliability).

- In the event of using the Sanken Products, you must use the same after carefully examining all applicable environmental laws and regulations that regulate the inclusion or use or both of any particular controlled substances, including, but not limited to, the EU RoHS Directive, so as to be in strict compliance with such applicable laws and regulations.

- You must not use the Sanken Products or the Information for the purpose of any military applications or use, including but not limited to the development of weapons of mass destruction. In the event of exporting the Sanken Products or the Information, or providing them for non-residents, you must comply with all applicable export control laws and regulations in each country including the U.S. Export Administration Regulations (EAR) and the Foreign Exchange and Foreign Trade Act of Japan, and follow the procedures required by such applicable laws and regulations.

- Sanken assumes no responsibility for any troubles, which may occur during the transportation of the Sanken Products including the falling thereof, out of Sanken's distribution network.

- Although Sanken has prepared this document with its due care to pursue the accuracy thereof, Sanken does not warrant that it is

error free and Sanken assumes no liability whatsoever for any and all damages and losses which may be suffered by you resulting

from any possible errors or omissions in connection with the Information.

- Please refer to our official website in relation to general instructions and directions for using the Sanken Products, and refer to the relevant specification documents in relation to particular precautions when using the Sanken Products.

- All rights and title in and to any specific trademark or tradename belong to Sanken and such original right holder(s).

DSGN-AEZ-16003