**MAX20361**

## **General Description**

The MAX20361 is a fully integrated solution for harvesting energy from single-/multi-cell solar sources. The device includes an ultra-low quiescent current (360nA) boost converter that is capable of starting from input voltages as low as 225mV (typ). In order to maximize the power extracted from the source, the MAX20361 implements a proprietary maximum power point tracking (MPPT) technique that allows efficient harvesting from  $15\mu W$  to over 300mW of available input power.

The MAX20361 also features an integrated charging and protection circuit that is optimized for Li-ion batteries, but can also be used to charge supercapacitors, thin-film batteries, or traditional capacitors. The charger features a programmable charging cut-off voltage with thresholds programmable through I<sup>2</sup>C interface as well as temperature shutoff.

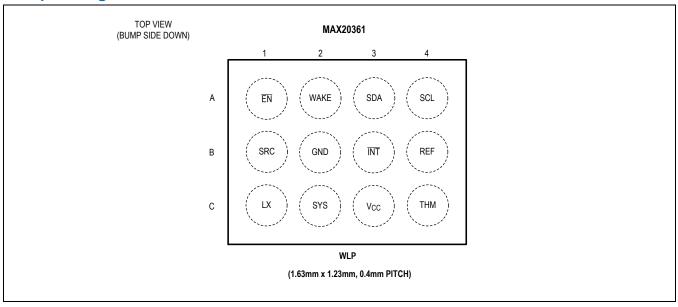

The MAX20361 is available in a 12-bump, 0.4mm pitch, 1.63mm x 1.23mm wafer-level package (WLP).

## **Applications**

- Wearable Fitness

- Medical Devices

- Industrial IoT Sensors

- Asset Tracking Devices

- · Wireless Sensor Networks

### **Benefits and Features**

- Single-/Multi-Cell Solar Energy Harvester

- 225mV to 2.5V (typ) Input-Voltage Range

- Efficient Harvesting from 15µW to Over 300mW of Available Input Power

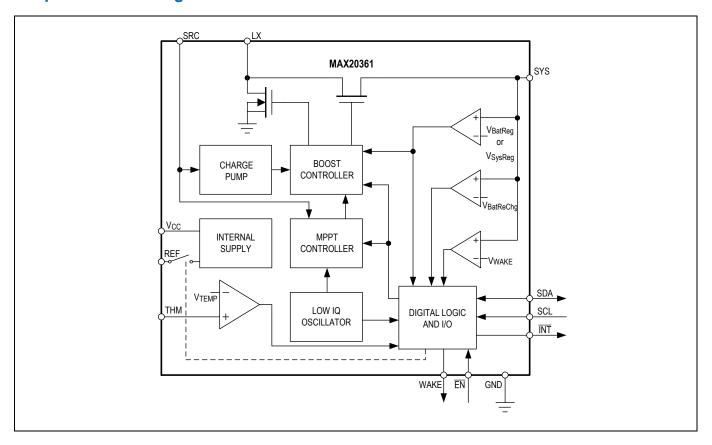

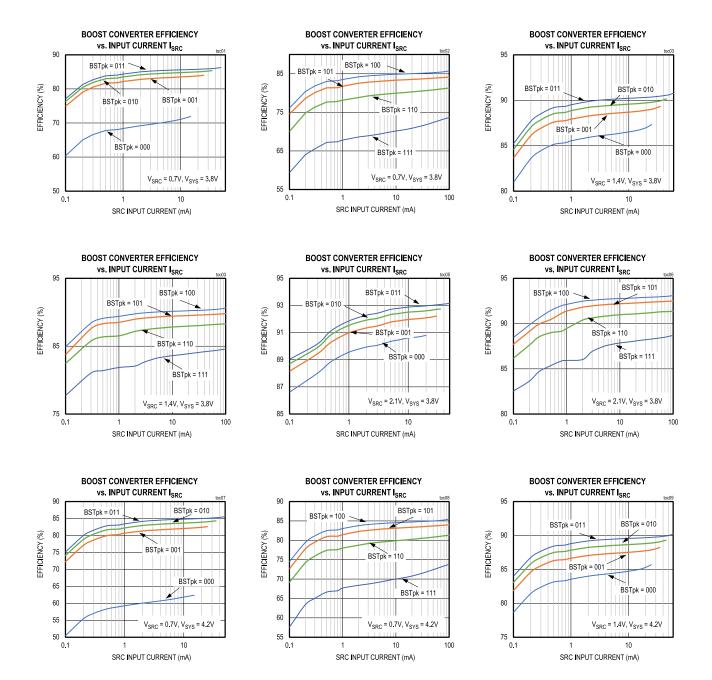

- 86% Efficiency at V<sub>SYS</sub> = 3.8V, I<sub>SRC</sub> = 30mA

- · Small Solution Size

- Utilizes Small 2016 4.7µH Inductor

- Maximum Power Point Tracking (MPPT) Technique Using Fractional VOC Method

- Programmable Fractional VOC Regulation Point through I<sup>2</sup>C Interface

- · Battery/Supercapacitor Charger

- Programmable Battery Termination Voltage through I<sup>2</sup>C Interface

- Programmable Power Good Wake-Up Signal Output Threshold through I<sup>2</sup>C Interface

Ordering Information appears at end of data sheet

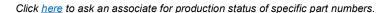

# **Simplified Block Diagram**

# **Absolute Maximum Ratings**

| SYS, V <sub>CC</sub> to GND                                               | -0.3V to +6V                     |

|---------------------------------------------------------------------------|----------------------------------|

| SRC to GND                                                                | -0.3V to +3.5V                   |

| $\overline{\text{INT}},\overline{\text{EN}},\text{SDA},\text{SCL}$ to GND | 0.3V to +6V                      |

| WAKE to GND                                                               | 0.3V to (SYS + 0.3V)             |

| REF, THM to GND                                                           | 0.3V to (V <sub>CC</sub> + 0.3V) |

| LX to GND                                                                 | 0.3V to (V <sub>CC</sub> + 0.3V) |

| Continuous Current into LX, GND                                           | or SYS0.5A to +0.5A              |

| Continuous Current into any other Pin0.05/                                        | A to +0.05A |

|-----------------------------------------------------------------------------------|-------------|

| Continuous Power Dissipation (Multilayer Board) (T derate 13.73mW/°C above +70°C) |             |

| Operating Temperature Range40º                                                    | °C to +85°C |

| Junction Temperature Range40°C                                                    | to +150°C   |

| Storage Temperature Range40°C                                                     | to +150°C   |

| Soldering Temperature (reflow)                                                    | +260°C      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### **12-WLP**

| Package Code                           | W121C1+2                       |  |  |

|----------------------------------------|--------------------------------|--|--|

| Outline Number                         | <u>21-100426</u>               |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |

| THERMAL RESISTANCE, FOUR LAYER BOARD   |                                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 72.82°C/W                      |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{SYS} = +3.0 \text{V to } +4.2 \text{V}, V_{SRC} = +0.3 \text{V to } +2.5 \text{V}, \text{ typical value is at } V_{SYS} = +3.8 \text{V}, V_{SRC} = +0.6 \text{V}, T_A = +25 ^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                           | SYMBOL                       | COND                                                                            | ITIONS                                                                                                              | MIN          | TYP      | MAX          | UNITS |

|-----------------------------------------------------|------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------|----------|--------------|-------|

| SUPPLY                                              |                              |                                                                                 |                                                                                                                     |              |          |              |       |

| SYS Shutdown Supply<br>Current                      | ISYS_SHDN                    | DeviceEnb = 1, any                                                              | V <sub>SRC</sub>                                                                                                    |              | 190      | 650          | nA    |

| SYS Sleep Supply<br>Current                         | I <sub>SYS_SLEEP</sub>       | DeviceEnb = 0, V <sub>SR</sub>                                                  | C = 0V                                                                                                              |              | 360      | 1200         | nA    |

| SYS Idle Supply Current                             | ISYS_IDLE                    | EN = 0V, boost not s                                                            | switching, not in sleep                                                                                             |              | 1.43     |              | μA    |

| SYSTEM CONTROL (SY                                  | S)                           |                                                                                 |                                                                                                                     |              |          |              |       |

| System Termination<br>Voltage-Programmable<br>Range | V <sub>SYS_REG</sub>         | 50mV steps, prograr                                                             | mmable through I <sup>2</sup> C                                                                                     |              | 4 to 4.7 |              | V     |

| System Regulation-<br>Voltage Accuracy              | V <sub>SYS_REG_AC</sub><br>C | $T_A = 0^{\circ}C \text{ to } +60^{\circ}C$                                     | SysReg[3:0] = 7,<br>SYS rising                                                                                      | -1           |          | +1           | %     |

| WAKE Voltage-<br>Programmable Range                 | VWAKE_RANG<br>E              | 100mV steps, progra                                                             | ammable through I <sup>2</sup> C                                                                                    |              | 3 to 3.7 |              | V     |

| WAKE Voltage<br>Accuracy                            | Vwake_acc                    |                                                                                 | WakeThr[2:0] = 0,<br>SYS rising                                                                                     | -2           |          | +2           | %     |

| WAKE Debounce Time                                  | twake_tdeb                   |                                                                                 |                                                                                                                     | 7 x<br>Tmeas |          | 8 x<br>Tmeas | ms    |

| BOOST REGULATOR                                     |                              |                                                                                 |                                                                                                                     |              |          |              |       |

| Input Operating Voltage at SRC                      | V <sub>SRC_RANGE</sub>       |                                                                                 |                                                                                                                     | 0            |          | 2.5          | V     |

| Minimum Cold-Start<br>Voltage                       | V <sub>SC</sub>              | T <sub>A</sub> = 25°C (Note 3)                                                  | T <sub>A</sub> = 25°C (Note 3)                                                                                      |              |          | 350          | mV    |

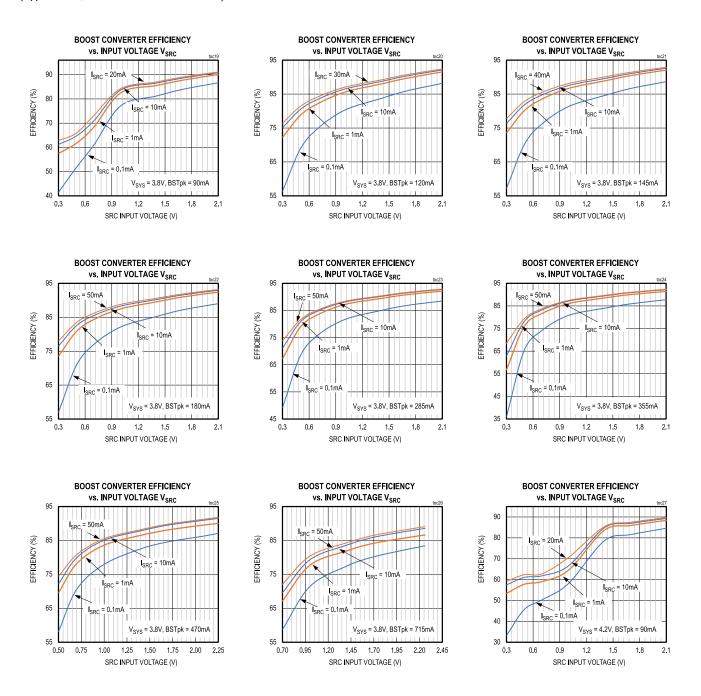

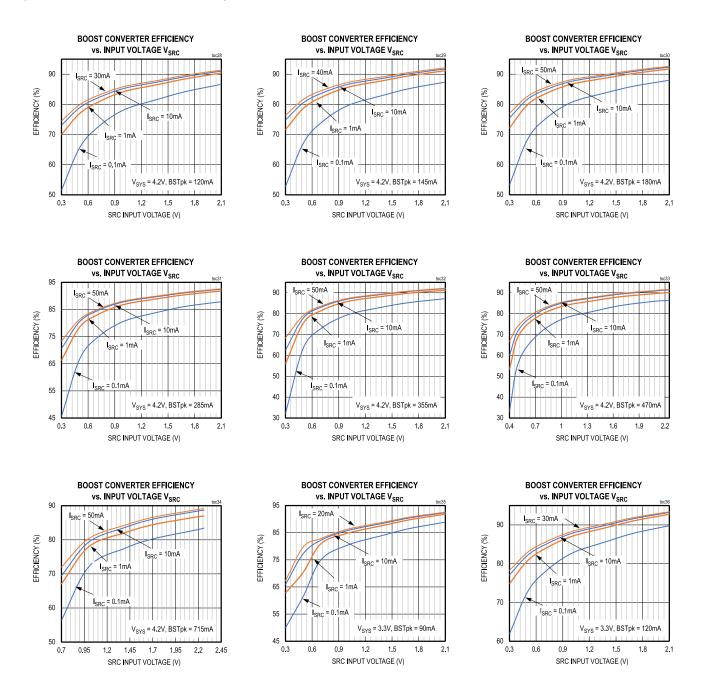

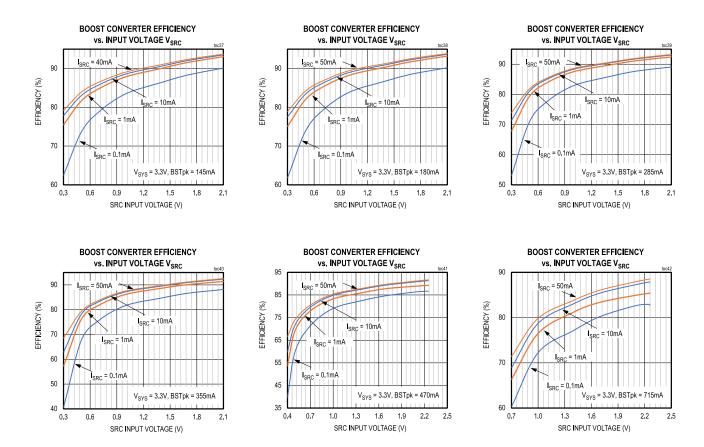

| Efficiency                                          | BOOST_EFF                    | I <sub>SRC</sub> = 100µA, L = 4<br>4R7M = P2 Series Ir                          | $V_{SRC} = 0.75V$ , $V_{SYS} = 3.8V$ , $I_{SRC} = 100\mu A$ , $L = 4.7\mu H$ , DFE201612E-4R7M = P2 Series Inductor |              |          |              | %     |

| Emoleroy                                            | BOOGT_ETT                    | $V_{SRC}$ = 0.75V, $V_{SYS}$<br>$I_{SRC}$ = 30mA, L = 4.<br>4R7M = P2 Series Ir | 7μH, DFE201612E-                                                                                                    |              | 86       |              | 70    |

| LX Low-Side On<br>Resistance                        | R <sub>ON_LXL</sub>          |                                                                                 |                                                                                                                     |              | 0.1      | 0.14         | Ω     |

| LX SYS High-Side On Resistance                      | R <sub>ON_LX_SYS</sub>       |                                                                                 |                                                                                                                     |              | 0.29     | 0.39         | Ω     |

| SRC LX Slow Snubber<br>Resistance                   | R <sub>LX_SSNUB</sub>        |                                                                                 |                                                                                                                     |              | 20       |              | kΩ    |

| SRC LX Snubber<br>Resistance                        | R <sub>LX_SNUB</sub>         |                                                                                 |                                                                                                                     |              | 342      |              | Ω     |

|                                                     | I <sub>BSTpk0</sub>          |                                                                                 |                                                                                                                     |              | 90       |              |       |

|                                                     | I <sub>BSTpk1</sub>          |                                                                                 |                                                                                                                     |              | 120      |              |       |

|                                                     | I <sub>BSTpk2</sub>          |                                                                                 |                                                                                                                     |              | 145      |              |       |

|                                                     | I <sub>BSTpk3</sub>          |                                                                                 |                                                                                                                     |              | 180      |              |       |

| Peak Current                                        | I <sub>BSTpk4</sub>          |                                                                                 |                                                                                                                     |              | 285      |              | mA    |

|                                                     | I <sub>BSTpk5</sub>          |                                                                                 |                                                                                                                     |              | 355      |              |       |

|                                                     | I <sub>BSTpk6</sub>          |                                                                                 |                                                                                                                     |              | 470      |              |       |

|                                                     | I <sub>BSTpk7</sub>          |                                                                                 |                                                                                                                     |              | 715      |              |       |

| SRC METER                                           |                              |                                                                                 |                                                                                                                     |              |          |              |       |

$(V_{SYS} = +3.0 \text{V to } +4.2 \text{V}, V_{SRC} = +0.3 \text{V to } +2.5 \text{V}, \text{ typical value is at } V_{SYS} = +3.8 \text{V}, V_{SRC} = +0.6 \text{V}, T_A = +25 ^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                                | SYMBOL                                                 | COND                                                                                                                                          | ITIONS                                                                    | MIN            | TYP                     | MAX  | UNITS             |

|----------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------|-------------------------|------|-------------------|

| SRC DAC Full-Scale                                       | V <sub>DACFS</sub>                                     | SRC equivalent volta                                                                                                                          | age                                                                       |                | 2.595                   |      | V                 |

| SRC Leakage                                              | I <sub>LNKSRC</sub>                                    | V <sub>SRC</sub> = 1V                                                                                                                         |                                                                           |                | 0.75                    |      | μA                |

| MAXIMUM POWER POI                                        | NT TRACKING                                            |                                                                                                                                               |                                                                           |                |                         |      |                   |

| Fractional Open Circuit<br>Voltage-Programmable<br>Range | V <sub>FRAC_VOC_P</sub>                                | 1.5% steps, program                                                                                                                           | mable through I <sup>2</sup> C                                            |                | 42.5 to<br>89.0         |      | %                 |

| Error of Fractional VOC<br>Regulation Point              | VFRAC_VOC_E<br>RROR                                    | V <sub>SRC</sub> = 0.6V,<br>includes<br>measurement error<br>of VOC and input<br>voltage regulation<br>error, excludes<br>SRC ripple (Note 3) | VOC[7:0] = 75,<br>Frac[4:0] = 25,<br>BSTpk = 3, I <sub>SRC</sub> =<br>1mA | -4.7           |                         | +4.7 | %                 |

|                                                          |                                                        | ATper = 0, Tper = 00                                                                                                                          | , see text                                                                |                | 64 *                    |      |                   |

| Open Circuit<br>Measurement Period                       | tFRAC_VOC                                              | ATper = 0, Tper = 01                                                                                                                          |                                                                           |                | Tmeas<br>128 *<br>Tmeas |      | s                 |

|                                                          |                                                        | ATper = 0, Tper = 10                                                                                                                          | , see text                                                                | 256 *<br>Tmeas |                         |      |                   |

|                                                          |                                                        | ATmeas = 0, Tmeas                                                                                                                             | ATmeas = 0, Tmeas = 00, see text                                          |                | 50                      |      |                   |

| Open Circuit Measurement Settling Time                   | t <sub>FRAC_VOC_S</sub><br>ETTLE                       | ATmeas = 0, Tmeas                                                                                                                             |                                                                           | 100            |                         | 1    |                   |

|                                                          |                                                        | ATmeas = 0, Tmeas                                                                                                                             | 250<br>500                                                                |                |                         | ms   |                   |

| Time                                                     |                                                        | ATmeas = 0, Tmeas                                                                                                                             |                                                                           |                |                         |      |                   |

| ĒN                                                       |                                                        |                                                                                                                                               |                                                                           | l              |                         |      |                   |

| <del></del>                                              | V <sub>ILENB</sub>                                     |                                                                                                                                               |                                                                           |                |                         | 0.4  | V                 |

| EN Input Threshold                                       | V <sub>IHENB</sub>                                     |                                                                                                                                               |                                                                           | 1.0            |                         |      |                   |

| EN Input Resistance                                      | R <sub>ENB</sub>                                       |                                                                                                                                               |                                                                           | 0.7            | 1                       | 1.3  | ΜΩ                |

| SCL, SDA, INT                                            |                                                        |                                                                                                                                               |                                                                           |                |                         |      | 1                 |

| SDA and INT Output-<br>Low Voltage                       | V <sub>OLSDA</sub> ,<br>V <sub>OLĪNT</sub>             | I = 5mA                                                                                                                                       |                                                                           |                |                         | 0.3  | V                 |

| SDA, SCL, INT Input<br>Current                           | I <sub>SDA</sub> , I <sub>SCL</sub> , I <sub>INT</sub> | V_ from 0V to 5.5V                                                                                                                            |                                                                           | -1             | 0                       | +1   | μA                |

| WAKE                                                     |                                                        |                                                                                                                                               |                                                                           |                |                         |      | 1                 |

| WAKE Output-Low<br>Voltage                               | V <sub>OLWAKE</sub>                                    | I = 5mA                                                                                                                                       |                                                                           |                |                         | 0.3  | V                 |

| WAKE Output-High<br>Voltage                              | VOHWAKE                                                | I = -5mA                                                                                                                                      |                                                                           | SYS -<br>0.3   |                         |      | V                 |

| THERMAL MONITORING                                       | G (REF, THM)                                           |                                                                                                                                               |                                                                           |                |                         |      |                   |

| REF Voltage                                              | V <sub>REF</sub>                                       | I <sub>REF</sub> from 0µA to 10                                                                                                               | 0μΑ                                                                       | 1.15           | 1.2                     | 1.25 | V                 |

| Cold Temperature Trip-<br>Point Programmable<br>Range    | V <sub>COLD</sub>                                      |                                                                                                                                               |                                                                           | 53.5           | 57.5                    | 60   | %V <sub>REF</sub> |

| Hot Temperature Trip-<br>Point Programmable<br>Range     | V <sub>HOT</sub>                                       |                                                                                                                                               |                                                                           | 16.2           | 18.7                    | 22   | %V <sub>REF</sub> |

| THM Input Leakage                                        | I <sub>THM</sub>                                       |                                                                                                                                               |                                                                           | -1             |                         | +1   | μA                |

| I <sup>2</sup> C INTERFACE                               | · ·                                                    | 1                                                                                                                                             |                                                                           | 1              |                         |      | <u> </u>          |

$(V_{SYS} = +3.0 \text{V to } +4.2 \text{V}, V_{SRC} = +0.3 \text{V to } +2.5 \text{V}, \text{ typical value is at } V_{SYS} = +3.8 \text{V}, V_{SRC} = +0.6 \text{V}, T_A = +25 ^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                       | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------|------------|-----|-----|-----|-------|

| SCL and SDA Input                               | V <sub>IL</sub>     |            |     |     | 0.4 |       |

| Threshold                                       | V <sub>IH</sub>     |            | 1   |     |     | V     |

| I <sup>2</sup> C TIMINGS                        |                     |            |     |     |     |       |

| Serial Operating<br>Frequency                   | f <sub>SCL</sub>    |            |     |     | 400 | kHz   |

| Maximum Clock Period                            | <sup>t</sup> SCLMAX |            | 2.5 |     |     | μs    |

| START Condition Hold<br>Time                    | t <sub>HD:STA</sub> |            | 0.6 |     |     | μs    |

| Clock Low Period                                | t <sub>LOW</sub>    |            | 1.3 |     |     | μs    |

| Clock High Period                               | <sup>t</sup> HIGH   |            | 0.6 |     |     | μs    |

| START Condition Setup<br>Time                   | t <sub>SU:STA</sub> |            | 0.6 |     |     | μs    |

| Repeat START Condition Setup Time               | t <sub>SU:STA</sub> |            | 0.6 |     |     | μs    |

| Data Hold Time                                  | t <sub>HD:DAT</sub> |            |     |     | 0   | ns    |

| Data Valid to SCL Rise<br>Time                  | t <sub>SU:DAT</sub> |            | 100 |     |     | ns    |

| STOP Condition Setup<br>Time                    | tsu:sto             |            | 0.6 |     |     | μs    |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |            | 1.3 |     |     | μs    |

Note 1: All devices 100% productions tested at 25°C. Limits over the operating temperature range are guaranteed by design.

**Note 2:** All capacitance values listed in this document refer to effective capacitance. Be sure to specify capacitors that meets these requirements under typical system operating conditions, taking into consideration the effects of voltage and temperature.

Note 3: Not production tested. Guaranteed by design.

# **Typical Operating Characteristics**

(T<sub>A</sub> = 25°C, unless otherwise noted.)

(T<sub>A</sub> = 25°C, unless otherwise noted.)

(T<sub>A</sub> = 25°C, unless otherwise noted.)

$(T_A = 25^{\circ}C, unless otherwise noted.)$

(T<sub>A</sub> = 25°C, unless otherwise noted.)

# **Bump Configuration**

# **Pin Descriptions**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                               |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | ĒN              | Active Low Enable Input. When $\overline{\text{EN}}$ is high the device stops switching and enters a low power state. $\overline{\text{EN}}$ is internally pulled down to GND by a 1M $\Omega$ resistor. In the shutdown state, I <sup>2</sup> C is still operational. |

| A2  | WAKE            | Wake Signal for System MCU. This push-pull output is asserted when SYS is above WakeThr[2:0] and the device is not in sleep mode.                                                                                                                                      |

| A3  | SDA             | I <sup>2</sup> C Serial Data                                                                                                                                                                                                                                           |

| A4  | SCL             | I <sup>2</sup> C Serial Clock                                                                                                                                                                                                                                          |

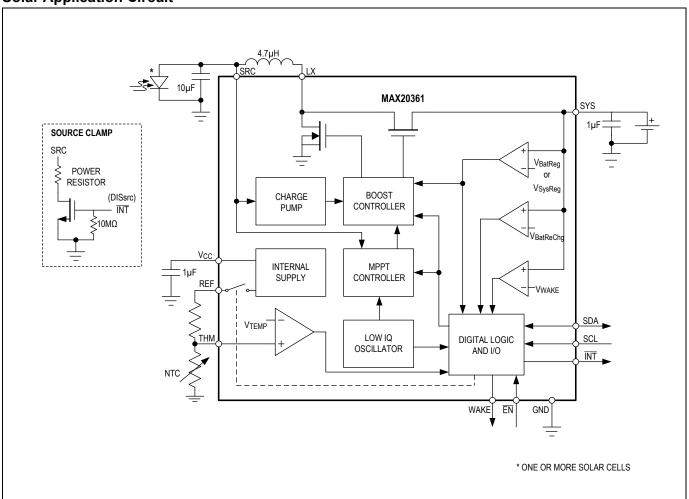

| B1  | SRC             | Source Input. Connect the harvesting source power output to SRC. Connect a 10 µF capacitor between SRC and GND.                                                                                                                                                        |

| B2  | GND             | Ground                                                                                                                                                                                                                                                                 |

| В3  | ĪNT             | Open-Drain Interrupt Output                                                                                                                                                                                                                                            |

| B4  | REF             | Internal-Voltage Reference                                                                                                                                                                                                                                             |

| C1  | LX              | Boost-Converter Switching Node. Connect a 4.7µH inductor between LX and the harvesting source power output (e.g., anode of solar cell).                                                                                                                                |

| C2  | SYS             | System Output. Connect to system input of power management IC. Connect a 1µF bypass capacitor between SYS and GND.                                                                                                                                                     |

| C3  | V <sub>CC</sub> | Internal Supply. Connect a 1µF bypass capacitor between V <sub>CC</sub> and GND.                                                                                                                                                                                       |

| C4  | THM             | Thermistor Input. Connect THM to a voltage divider formed by a pullup resistor and a pulldown thermistor.                                                                                                                                                              |

## **Detailed Description**

The MAX20361 is a fully integrated solution for harvesting energy from single-/multi-cell solar sources. The device includes an ultra-low quiescent-current boost converter that is capable of starting from input voltage as low as 225mV (typ). In order to maximize the power extracted from the source, the MAX20361 implements a proprietary maximum power point tracking (MPPT) technique that allows efficient harvesting from 15µW to over 300mW of available input power.

The MAX20361 also features an integrated charging and protection circuit that is optimized for Li-ion batteries, but can also be used to charge supercapacitors, thin-film batteries, or traditional capacitors. The charger features a programmable charging cut-off voltage with thresholds programmable through the I<sup>2</sup>C interface as well as temperature shutoff.

#### **Boost Converter**

The MAX20361 boost converter is optimized to efficiently harvest energy from a single-/multi-cell solar source. The MAX20361 implements a boost converter, which collects the current from the low-voltage SRC input and transfers it to the higher-voltage SYS output.

The switching frequency is not fixed but changes with the SRC voltage, SYS voltage and inductance values. Each time the SRC voltage drops below its regulation point, the boost is halted. SRC capacitance is needed to reduce the SRC ripple, but its value is not critical for stability (see the *Applications Information* section for more details).

The SYS voltage is monitored and when it reaches the regulation point, the boost is halted to avoid overcharging of the the battery, or an overvoltage on the SYS node.

### **Harvesting Meter**

The MAX20361 reports the count of the switching cycles of the boost converter during the last Tmeas[5:4](0x07) time in the HarvCntH(0x0A) and HarvCntL(0x0B) registers. This "harvesting count" is proportional to the current harvested during that period. To avoid a false read, the update of HarvCntH and HarvCntL is inhibited if the boost was halted in the last Tmeas period due to thermal monitoring, open-circuit voltage measurement, SYS overvoltage detected, sleep mode or I<sup>2</sup>C commands.

Every time a new valid value of HarvCntH/L is loaded, the HARrdy[4](0x01) bit is set.

### **Maximum Power Point Tracking (MPPT)**

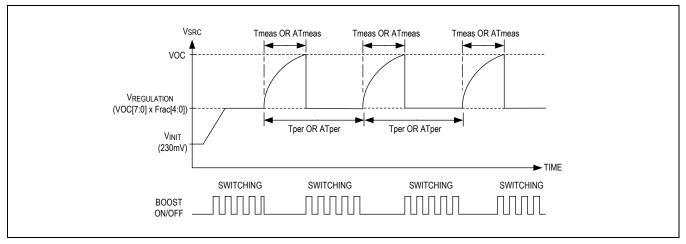

During normal operation, the MAX20361 automatically measures the open-circuit voltage and computes the optimal SRC voltage to transfer the maximum power from the solar cell. Every Tper[1:0](0x07) (by default 64 x Tmeas, with Tmeas = 50ms, every 3.2s), or when requested by  $I^2C$ , the internal boost is halted for Tmeas[5:4](0x07) and the SRC voltage is measured with the internal 8-bit ADC.

The SRC regulation point is computed by multiplying the measured voltage at SRC by the Frac[4:0](0x06) field. At power-up, the MAX20361 regulates the SRC voltage at a level determined by the value of Frac[4:0] and the default value of VOC[7:0]. (For example, if Frac[4:0] is set to 80% and the default value of VOC[7:0] is 29 decimal, the SRC regulation voltage is 230mV typical, which is 80% of 290mV) until the first VOC measure or an  $I^2C$  write on VOC[7:0] register is performed. Refer to Figure 1 for the operation of  $V_{SRC}$  during MPPT.

To adapt the SRC measurement time, if the ATmeas[3](0x07) bit is set, the MAX20361 modulates the measurement time based on the last measured "harvesting count" (HarvCntH/L registers), as specified in  $\underline{\textit{Table 1}}$  below.

Table 1. Measurement Time Based on Harvesting Count

| HARVESTING COUNT VALUE | USED MEASUREMENT TIME |

|------------------------|-----------------------|

| Less than 13           | 2 x Tmeas             |

| Between 13 and 26      | Tmeas                 |

| Between 26 and 52      | Tmeas / 2             |

| Above 52               | Tmeas / 4             |

The MAX20361 automatically adapts the measurement period when the ATper[2](0x07) bit is set. After power-on reset, the device ignores the first result of harvesting count and stores the second result in the HarvCntH and HarvCntL registers.

If any future harvesting count is greater or lower than the existing stored harvesting count by a factor of 2, the Tper timer is reset and a new VOC measurement is forced immediately.

A VOC measurement can be requested through the FrcMeas[7](0x07) bit. The measurement starts within Tmeas and results are stored in the VOCMeas(0x09) register, and VOCrdy[3](0x01) bit is set with the corresponding interrupt.

Figure 1. VSRC During Maximum Power Point Tracking

### **Low-Light Sleep Mode**

To save power, the MAX20361 enters sleep mode when the harvesting meter value is below SlpThd[7:0](0x0C) threshold (default 0x00) or when VOC[7:0] is set below the default VOC value by either the VOC measurement or a direct I<sup>2</sup>C write to it. In sleep mode, the internal reference, the boost and the THM monitor are turned off, and SYS and THM are not monitored, and WAKE output is forced low. The MAX20361 remains in sleep mode until the next VOC or THM measurement, or a write to VOC[7:0] with a value equal or above the default VOC value. Low-power mode is inhibited during cold startup.

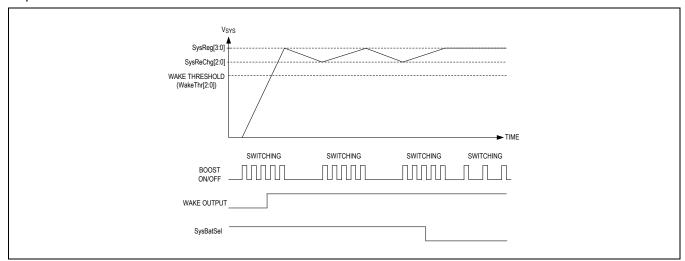

#### **WAKE Output**

Except in Shutdown or Sleep modes, the MAX20361 monitors the SYS output. When SYS is above the WAKE threshold for at least 7 to 8 x Tmeas (typ), the WAKE output is asserted (and the WAKEbSt[0](0x01) bit is set to 0). When the device goes into Sleep or Shutdown mode, WAKE output is forced low. Refer to  $\underline{\textit{Figure 2}}$  for the waveform of V<sub>SYS</sub> and WAKE output.

Figure 2. Waveform of VSYS and WAKE Output

#### **Thermal Monitor**

When ThmEn[3](0x08) is 1, the MAX20361 monitors the voltage on THM. The device checks  $V_{THM}$  once if FrcTHM[6](0x07) is 1 or periodically every Tper[1:0](0x07) time if THMper[6](0x05) is 1. During that process, the MAX20361 drives REF to 1.2V (typ) for 1ms (typ). The voltage divider, formed by the pullup resistor from THM to REF and the NTC thermistor from THM to ground, provides a voltage at THM proportional to the temperature as a fraction of  $V_{REF}$ . When  $V_{THM}$  is above 57.5% of  $V_{REF}$  or below 18.7% of  $V_{REF}$ , THMflag[6](0x01) is set and the boost is halted. These thresholds are equivalent to 0°C and 45°C if a 10k $\Omega$  NTC thermistor with  $\beta$  = 3380 and a 22k $\Omega$  pullup resistor are used.

The device also performs a THM check at power-on and on the  $\overline{\text{EN}}$  falling edge. A fault condition is assumed until this first THM check is completed.

#### **Shutdown**

The device enters Shutdown mode when the  $\overline{\text{EN}}$  pin is high or DeviceEnb[1](0x08) is 1. In this condition, current consumption is minimized, SYS, THM and SRC are not monitored, WAKE output is forced low and the internal oscillator is turned off. All internal logic, except those values under I<sup>2</sup>C, is held in reset. In the shutdown state, only the POR on V<sub>CC</sub> is active, and the V<sub>CC</sub>-SYS switch is left open until V<sub>CC</sub> is above the POR threshold. The device exits Shutdown mode when  $\overline{\text{EN}}$  is low and DeviceEnb is 0.

### **Cold-Startup**

The cold start feature of the MAX20361 allows the device to start up even if  $V_{SYS}$  is below the wake threshold or absent. For a cold startup, the device initially uses a low power charge pump to charge up  $V_{CC}$  from the power source (such as a solar cell) on SRC while SYS is not charged. Once  $V_{CC}$  is charged above the POR level, the internal references are enabled and the main boost takes over from the charge pump. As the main boost continues to charge,  $V_{CC}$  and SYS gets charged above the wake threshold, the  $V_{CC}$ -SYS switch is closed and the device is powered from SYS. This completes the cold startup, and the normal operation of the device assumes.

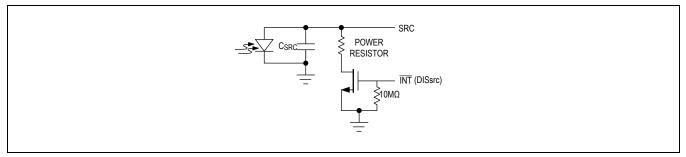

### **Source Clamp**

By the DISintb[4](0x05) bit, the INT output can be reconfigured as a push-pull DISsrc output to drive an external clamp circuit used to prevent overvoltage on SRC. The clamp circuit (see <u>Figure 3</u>) can be formed by an external nMOS and a load resistor. When the clamp circuit is turned on, the SRC is discharged through the external load resistor. When the boost converter is enabled, the DISsrc is driven to divert excess input current in order to let SRC regulate. In shutdown mode, the DISsrc output is driven statically high. The DISsrc output is disabled during VOC measurement and sleep mode. Refer to the <u>nMOS Transistor Selection</u> section.

Figure 3. Source Clamp Circuitry

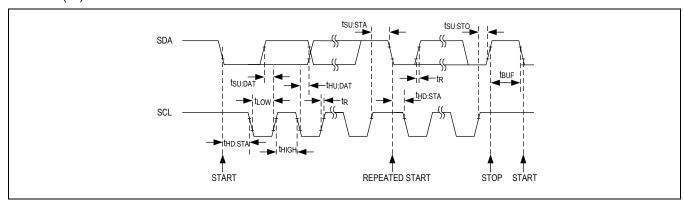

### I<sup>2</sup>C Interface

The MAX20361 contains an I<sup>2</sup>C-compatible interface for data communication with a host controller (SCL and SDA). The interface supports a clock frequency of up to 400kHz. SCL and SDA require pullup resistors that are connected to a positive supply.

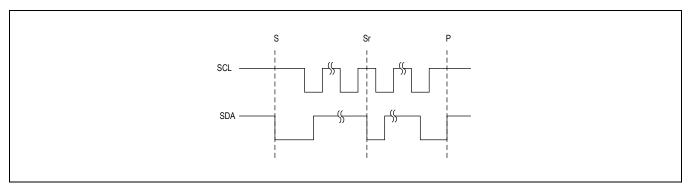

When writing to the MAX20361 using I<sup>2</sup>C, the master sends a START condition (S) followed by the MAX20361 I<sup>2</sup>C address. After the address, the master sends the register address of the register that is to be programmed. The master then ends communication by issuing a STOP condition (P) to relinquish control of the bus, or a REPEATED START condition (Sr) to communicate to another I<sup>2</sup>C slave.

Figure 4. I<sup>2</sup>C Interface Timing

Figure 5. I<sup>2</sup>C START, STOP, and REPEATED START Conditions

#### **Slave Address**

Set the Read/Write bit high to configure the MAX20361 to read mode (see <u>Table 2</u>). Set the Read/Write bit low to configure the MAX20361 to write mode. The address is the first byte of information sent to the MAX20361 after the START condition.

Table 2. I<sup>2</sup>C Slave Addresses

| ADDRESS FORMAT | HEX  | BINARY   |

|----------------|------|----------|

| 7-Bit Slave ID | 0x15 | 0010101  |

| Write Address  | 0x2A | 00101010 |

| Read Address   | 0x2B | 00101011 |

#### **Bit Transfer**

One data bit is transferred on the rising edge of each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the Start, Stop, And Repeated Start Conditions section). Both SDA and SCL remain high when the bus is not active.

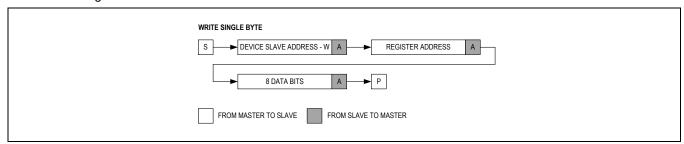

### Single-Byte Write

In this operation, the master sends an address and two data bytes to the slave device. The following procedure describes the single byte write operation:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address plus a write bit (low).

- 3. The addressed slave asserts an ACK on the data line.

- 4. The master sends the 8-bit register address.

- 5. The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6. The master sends 8 data bits.

- 7. The slave asserts an ACK on the data line.

- 8. The master generates a STOP condition.

Figure 6. Write Byte Sequence

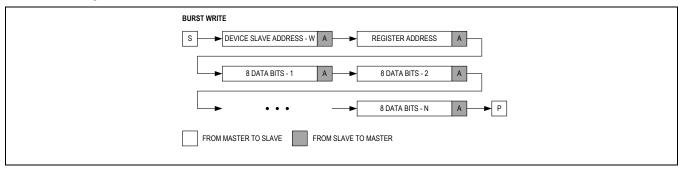

#### **Burst Write**

In this operation, the master sends an address and multiple data bytes to the slave device. The slave device automatically increments the register address after each data byte is sent. The following procedure describes the burst write operation:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address plus a write bit (low).

- 3. The addressed slave asserts an ACK on the data line.

- 4. The master sends the 8-bit register address.

- 5. The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6. The master sends eight data bits.

- 7. The slave asserts an ACK on the data line.

- 8. Repeat 6 and 7 N-1 times.

- 9. The master generates a STOP condition.

Figure 7. Burst Write Sequence

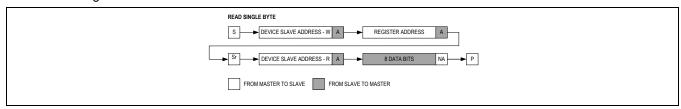

### Single Byte Read

In this operation, the master sends an address plus two data bytes and receives one data byte from the slave device. The following procedure describes the single byte read operation:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address plus a write bit (low).

- 3. The addressed slave asserts an ACK on the data line.

- 4. The master sends the 8-bit register address.

- 5. The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6. The master sends a REPEATED START condition.

- 7. The master sends the 7-bit slave address plus a read bit (high).bz

- 8. The addressed slave asserts an ACK on the data line.

- 9. The slave sends eight data bits.

- 10. The master asserts a NACK on the data line.

- 11. The master generates a STOP condition.

Figure 8. Read Byte Sequence

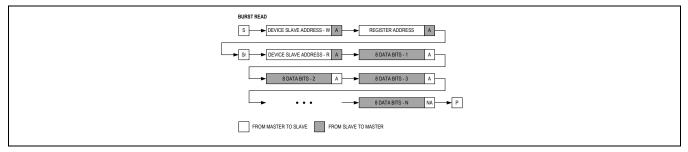

#### **Burst Read**

In this operation, the master sends an address plus two data bytes and receives multiple data bytes from the slave device. The following procedure describes the burst byte read operation:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address plus a write bit (low).

- 3. The addressed slave asserts an ACK on the data line.

- 4. The master sends the 8-bit register address.

- 5. The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6. The master sends a REPEATED START condition.

- 7. The master sends the 7-bit slave address plus a read bit (high).

- 8. The slave asserts an ACK on the data line.

- 9. The slave sends eight data bits.

- 10. The master asserts an ACK on the data line.

- 11. Repeat 9 and 10 N-2 times.

- 12. The slave sends the last eight data bits.

- 13. The master asserts a NACK on the data line.

- 14. The master generates a STOP condition.

Figure 9. Burst Read Sequence

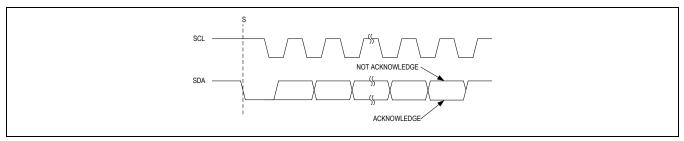

## **Acknowledge Bits**

Data transfers are acknowledged with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX20361 generate ACK bits. To generate an ACK, pull SDA low before the rising edge of the ninth clock pulse and hold it low during the high period of the ninth clock pulse. To generate a NACK, leave SDA high before the rising edge of the ninth clock pulse and leave it high for the duration of the ninth clock pulse. Monitoring for NACK bits allows for detection of unsuccessful data transfers.

Figure 10. Acknowledge Bits

# **Register Map**

## MAX20361

| IVIAAZUU   | · · · · · · · · · · · · · · · · · · · |           |                         |           |           |             |             |              |            |

|------------|---------------------------------------|-----------|-------------------------|-----------|-----------|-------------|-------------|--------------|------------|

| ADDRESS    | NAME                                  | MSB       |                         |           |           |             |             |              | LSB        |

| User Regis | ters                                  |           |                         |           |           |             |             |              |            |

| 0x00       | DeviceID[7:0]                         |           | Chi                     | pID[3:0]  |           |             | ChipRe      | ev[3:0]      |            |

| 0x01       | Status[7:0]                           | VOCValid  | THMflag                 | HSYSFlag  | HARrdy    | VOCrdy      | Sleep       | ENbStat      | WAKEbSt    |

| 0x02       | Int[7:0]                              | -         | -                       | -         | HARrdyInt | VOCrdyInt   | VOCValidInt | EnbStatInt   | WakebStInt |

| 0x03       | IntMsk[7:0]                           | -         | -                       | -         | HARrdyMsk | VOCrdyMsk   | VOCValidMsk | EnbStatMsk   | WakebStMsk |

| 0x04       | SysRegCfg[7:0]                        | SysBatSel | SysBatSel SysReChg[2:0] |           |           | SysReg[3:0] |             |              |            |

| 0x05       | WakeCfg[7:0]                          | VOCper    | THMper                  | -         | DISintb   | -           |             | WakeThr[2:0] |            |

| 0x06       | MpptCfg[7:0]                          | -         | -                       | -         |           |             | Frac[4:0]   |              |            |

| 0x07       | MeasCfg[7:0]                          | FrcMeas   | FrcTHM                  | Tme       | as[1:0]   | ATmeas      | ATper       | Тре          | r[1:0]     |

| 0x08       | DevCntl[7:0]                          | -         |                         | BSTpk[2:0 | )]        | ThmEn       | FrcWAKE     | DeviceEnb    | BoostEnb   |

| 0x09       | VOCMeas[7:0]                          |           | VOC[7:0]                |           |           |             |             |              |            |

| 0x0A       | HarvCntH[7:0]                         |           | HARhigh[7:0]            |           |           |             |             |              |            |

| 0x0B       | HarvCntL[7:0]                         |           | HARlow[7:0]             |           |           |             |             |              |            |

| 0x0C       | SleepThd[7:0]                         |           |                         |           |           | SlpThd[7:0] |             |              |            |

## **Register Details**

## DeviceID (0x00)

| ВІТ         | 7 | 6     | 5      | 4 | 3            | 2    | 1    | 0 |  |

|-------------|---|-------|--------|---|--------------|------|------|---|--|

| Field       |   | Chipl | D[3:0] |   | ChipRev[3:0] |      |      |   |  |

| Reset       |   | 0:    | x1     |   | 0x1          |      |      |   |  |

| Access Type |   | Read  | Only   |   |              | Read | Only |   |  |

| BITFIELD | BITS | DESCRIPTION         |

|----------|------|---------------------|

| ChipID   | 7:4  | Chip Identification |

| ChipRev  | 3:0  | Chip Revision       |

## Status (0x01)

| BIT         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Field       | VOCValid  | THMflag   | HSYSFlag  | HARrdy    | VOCrdy    | Sleep     | ENbStat   | WAKEbSt   |

| Reset       | 0x0       |

| Access Type | Read Only |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOCValid | 7    | Indicates if at least one SRC open-circuit measurement was performed since the last V <sub>CC</sub> POR event. This bit is also reset when a write to the VOCMeas register is performed. This bit is not set after a VOC measurement.  0b0: No SRC open-circuit measurement was performed since the last V <sub>CC</sub> POR event. 0b1: At least one SRC open-circuit measurement was performed since the last V <sub>CC</sub> POR event. |

| THMflag  | 6    | THM Fault Status  0b0: No THM fault detected  0b1: THM fault detected during the last Tmeas period                                                                                                                                                                                                                                                                                                                                         |

| HSYSFlag | 5    | SysReg Overvoltage Fault Flag  0b0: V <sub>SYS</sub> is not over V <sub>SYS_REG</sub> 0b1: V <sub>SYS</sub> is over V <sub>SYS_REG</sub>                                                                                                                                                                                                                                                                                                   |

| HARrdy   | 4    | Harvest Meter Status  0b0: Harvest meter has not been updated since the last read of HarvCnth/L register.  0b1: Harvest meter has been updated since the last read of HarvCnth/L register.  Note: this bit is reset when the HarvCntH register is read.                                                                                                                                                                                    |

| VOCrdy   | 3    | Open-Circuit Voltage Status  0b0: No new open-circuit voltage measurement since the last read of VOCMeas register.  0b1: New open-circuit voltage available since the last read of VOCMeas register.                                                                                                                                                                                                                                       |

| Sleep    | 2    | Indicates if the Device is in Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                   |

| BITFIELD | BITS | DESCRIPTION                                                                                                            |

|----------|------|------------------------------------------------------------------------------------------------------------------------|

|          |      | 0b0: Device is not in sleep mode and it is harvesting. 0b1: Device is in sleep mode to save SYS power (no harvesting). |

|          |      | Indicates if the Device is in Shutdown (or Between ENb Pin Input and DeviceEnb Bit)                                    |

| ENbStat  | 1    | 0b0: ENb pin low and DeviceEnb bit set to 0.                                                                           |

|          |      | 0b1: ENb pin high or DeviceEnb bit set to 1.                                                                           |

|          |      | Indicates the Status of the WAKE Pin Output                                                                            |

|          |      | Only the SYS comparator; does not include the FrcWAKE).                                                                |

| WAKEbSt  | 0    | This bit is not valid if the Sleep flag is set.                                                                        |

|          |      | 0b0: WAKE pin high (SYS above WakeThr[2:0](0x05) threshold)                                                            |

|          |      | 0b1: WAKE pin low (SYS below WakeThr[2:0](0x05) threshold)                                                             |

## Int (0x02)

| BIT         | 7 | 6 | 5 | 4                  | 3                  | 2                  | 1                  | 0                  |

|-------------|---|---|---|--------------------|--------------------|--------------------|--------------------|--------------------|

| Field       | - | ı | _ | HARrdyInt          | VOCrdyInt          | VOCValidInt        | EnbStatInt         | WakebStInt         |

| Reset       | - | - | _ | 0x0                | 0x0                | 0x0                | 0x0                | 0x0                |

| Access Type | - | - | - | Read Clears<br>All |

| BITFIELD    | BITS | DESCRIPTION                                                            |

|-------------|------|------------------------------------------------------------------------|

|             |      | HARrdy Interrupt                                                       |

| HARrdyInt   | 4    | 0b0: No change in status of HARrdy<br>0b1: Change in status of HARrdy  |

|             |      | VOCrdy Interrupt                                                       |

| VOCrdyInt   | 3    | 0b0: No change in status of VOCrdy 0b1: Change in status of VOCrdy     |

|             |      | VOCValid Interrupt                                                     |

| VOCValidInt | 2    | 0b0: No change in status of VOCValid 0b1: Change in status of VOCValid |

|             |      | EnbStat Interrupt                                                      |

| EnbStatInt  | 1    | 0b0: No change in status of EnbStat 0b1: Change in status of EnbStat   |

| BITFIELD   | вітѕ | DESCRIPTION                                                                              |

|------------|------|------------------------------------------------------------------------------------------|

| WakebStInt | 0    | WakebSt Interrupt  0b0: No change in status of WakebSt  0b1: Change in status of WakebSt |

## IntMsk (0x03)

| ВІТ         | 7 | 6 | 5 | 4           | 3           | 2           | 1           | 0           |

|-------------|---|---|---|-------------|-------------|-------------|-------------|-------------|

| Field       | - | - | - | HARrdyMsk   | VOCrdyMsk   | VOCValidMsk | EnbStatMsk  | WakebStMsk  |

| Reset       | - | - | - | 0x0         | 0x0         | 0x0         | 0x0         | 0x0         |

| Access Type | - | - | - | Write, Read |

| BITFIELD    | вітѕ | DESCRIPTION                                                       |

|-------------|------|-------------------------------------------------------------------|

|             |      | HARrdyInt Interrupt Mask                                          |

| HARrdyMsk   | 4    | 0b0: HARrdy interrupt not masked<br>0b1: HARrdy interrupt masked  |

|             |      | VOCrdy Interrupt Mask                                             |

| VOCrdyMsk   | 3    | 0b0: VOCrdy interrupt not masked 0b1: VOCrdy interrupt masked     |

|             |      | VOCValid Interrupt Mask                                           |

| VOCValidMsk | 2    | 0b0: VOCValid interrupt not masked 0b1: VOCValid interrupt masked |

|             |      | EnbStat Interrupt Mask                                            |

| EnbStatMsk  | 1    | 0b0: EnbStat interrupt not masked 0b1: EnbStat interrupt masked   |

|             |      | WakebSt Interrupt Mask                                            |

| WakebStMsk  | 0    | 0b0: WakebSt interrupt not masked 0b1: WakebSt interrupt masked   |

# SysRegCfg (0x04)

| BIT   | 7         | 6 | 5             | 4 | 3 | 2           | 1 | 0 |  |  |

|-------|-----------|---|---------------|---|---|-------------|---|---|--|--|

| Field | SysBatSel |   | SysReChg[2:0] |   |   | SysReg[3:0] |   |   |  |  |

| Reset       | 0x0         | 0x0         | 0x7         |

|-------------|-------------|-------------|-------------|

| Access Type | Write, Read | Write, Read | Write, Read |

| BITFIELD  | BITS | DESCRIPTION                                                                                                                                                                                                                                |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |      | Selects Regulation Mode of SYS                                                                                                                                                                                                             |

| SysBatSel | 7    | 0b0: The boost attempts to regulate the SYS node at V <sub>SysReg</sub> .  0b1: The boost charges the SYS node until it reaches V <sub>SysReg</sub> and then switches off until SYS drops to V <sub>SysReg</sub> - V <sub>SysReChg</sub> . |

|           |      | Battery Recharge Threshold Voltage                                                                                                                                                                                                         |

| SysReChg  | 6:4  | 0b000: 25mV<br>0b001: 50mV<br>0b010: 75mV<br>0b011: 100mV<br>0b100: 150mV<br>0b101: 200mV<br>0b110: 250mV<br>0b111: 300mV                                                                                                                  |

| SysReg    | 3:0  | System Regulation or Battery Termination Voltage On the SYS Node  0b0000: 4.0V linear step, 50mV 0b1111: 4.75V                                                                                                                             |

## WakeCfg (0x05)

| BIT         | 7           | 6           | 5 | 4           | 3 | 2            | 1 | 0 |

|-------------|-------------|-------------|---|-------------|---|--------------|---|---|

| Field       | VOCper      | THMper      | - | DISintb     | - | WakeThr[2:0] |   |   |

| Reset       | 0x1         | 0x0         | - | 0x0         | - | 0x7          |   |   |

| Access Type | Write, Read | Write, Read | - | Write, Read | - | Write, Read  |   |   |

| BITFIELD | вітѕ | DESCRIPTION                                                                                                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | VOC Every Tper (Perform Open Circuit Measurement Every Tper Period)                                                                                               |

| VOCper   | 7    | 0b0: VOC measurement performed only on request 0b1: VOC measurement performed every "Tper" time Note: this bit also disables the first VOC measurement after POR. |

| THMper   | 6    | Thermal Monitor Every Tper                                                                                                                                        |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                 |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | 0b0: Thermal monitoring is not performed every Tper time. 0b1: Thermal monitoring is performed every Tper time (only if also ThmEn is set). |

|          |      | Disable the INTb Pin and Convert It Into a Push-Pull Output to Discharge SRC (Clamp SRC Voltage)                                            |

| DISintb  | 4    | 0b0: INTb is an open-drain output for interrupt.                                                                                            |

|          |      | 0b1: INTb becomes a DISsrc push-pull output (to V <sub>CC</sub> ). When high, discharge SRC through a resistor.                             |

|          |      | Wake Threshold. When BAT reaches this voltage, the device asserts the WAKE output.                                                          |

|          |      | 0b000: 3.0V                                                                                                                                 |

|          |      | 0b001: 3.1V                                                                                                                                 |

| WakeThr  | 2:0  | 0b010: 3.2V                                                                                                                                 |

| wakeiiii | 2.0  | 0b011: 3.3V                                                                                                                                 |

|          |      | 0b100: 3.4V                                                                                                                                 |

|          |      | 0b101: 3.5V                                                                                                                                 |

|          |      | 0b110: 3.6V                                                                                                                                 |

|          |      | 0b111: 3.7V                                                                                                                                 |

## MpptCfg (0x06)

| ВІТ         | 7 | 6 | 5 | 4    | 3 | 2           | 1 | 0 |

|-------------|---|---|---|------|---|-------------|---|---|

| Field       | _ | _ | _ |      |   | Frac[4:0]   |   |   |

| Reset       | _ | _ | - | 0x19 |   |             |   |   |

| Access Type | _ | _ | ı |      |   | Write, Read |   |   |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                   |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frac     | 4:0  | Set the Fraction of the Open-Circuit Voltage to which the Boost Converter Attempts to Regulate at V <sub>SRC</sub> .  0b00000: 42.5% Linear scale, 1.5% / LSB  0b11111: 89.0% |

## MeasCfg (0x07)

| BIT   | 7       | 6      | 5          | 4 | 3      | 2     | 1         | 0 |

|-------|---------|--------|------------|---|--------|-------|-----------|---|

| Field | FrcMeas | FrcTHM | Tmeas[1:0] |   | ATmeas | ATper | Tper[1:0] |   |

| Reset | 0x0     | 0x0    | 0x0        |   | 0x1    | 0x1   | 0x2       |   |

| Access Type | Write Only<br>Clears All | Write Only<br>Clears All | Write, Read | Write, Read | Write, Read | Write, Read |

|-------------|--------------------------|--------------------------|-------------|-------------|-------------|-------------|

|-------------|--------------------------|--------------------------|-------------|-------------|-------------|-------------|

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FrcMeas  | 7    | Writing 1 to this bit forces a measure of an open-circuit voltage measurement (if NoVOCMeas is 0) at SRC. This bit is automatically forced to 0.  The measurement algorithm and time for VOC at SRC is set by ATmeas and Tmeas bits.  Until FrcMeas is set, the VOC register should not be written.                                                    |

| FrcTHM   | 6    | Writing 1 to this bit forces a measure of thermal monitoring (only if ThmEn bit is 1). This bit is automatically forced to 0.                                                                                                                                                                                                                          |

| Tmeas    | 5:4  | Set the Measurement Time  0b00: 50ms 0b01: 100ms 0b10: 250ms 0b11: 500ms                                                                                                                                                                                                                                                                               |

| ATmeas   | 3    | Set the Algorithm Used to Adjust the Settling Time for VOC Measure  0b0: The settling time is fixed and set by Tmeas bits.  0b1: Adaptative measuring time based on the current HarvCnt value, from Tmeas / 4 to 2 x Tmeas.                                                                                                                            |

| ATper    | 2    | Adaptative Period (Valid Only If Tper < 0b11)  0b0: Disabled 0b1: Store HarvCntH/L after 2 x Tmeas (or more, see text). A measure is forced (if not in sleep) when the future harvesting value is greater or lower than the existing stored measurement by a factor of 2 (future HarvCnt/current HarvCnt < 0.5 or future HarvCnt/current HarvCnt > 2). |

| Tper     | 1:0  | Set the Period of Automatic Measurement  0b00: 64 x Tmeas 0b01: 128 x Tmeas 0b10: 256 x Tmeas 0b11: Disabled  When "Disabled", VOC and THM are never automatically read. The system should periodically use the FrcMeas and FrcTHM bit to force measurements.                                                                                          |

## DevCntl (0x08)

| ВІТ   | 7 | 6          | 5 | 4     | 3       | 2         | 1        | 0 |

|-------|---|------------|---|-------|---------|-----------|----------|---|

| Field | - | BSTpk[2:0] |   | ThmEn | FrcWAKE | DeviceEnb | BoostEnb |   |

| Reset       | 1 | 0x3         | 0x0         | 0x0         | 0x0         | 0x0         |

|-------------|---|-------------|-------------|-------------|-------------|-------------|

| Access Type | - | Write, Read |

| BITFIELD  | BITS | DESCRIPTION                                                                                                                       |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------|

|           |      | Select the Peak Current for The Boost Converter                                                                                   |

|           |      | 0b000: 90mA                                                                                                                       |

|           |      | 0b001: 120mA                                                                                                                      |

| BSTpk     | 6:4  | 0b010: 145mA                                                                                                                      |

| Вотрк     | 0.4  | 0b011: 180mA                                                                                                                      |

|           |      | 0b100: 285mA                                                                                                                      |

|           |      | 0b101: 355mA                                                                                                                      |

|           |      | 0b110: 470mA                                                                                                                      |

|           |      | 0b111: 715mA                                                                                                                      |

|           |      | Thermal Monitoring Enable Bit                                                                                                     |

|           |      | 0b0: Thermal monitoring is not enabled, and temperature does not affect boost                                                     |

| ThmEn     | 3    | operation.                                                                                                                        |

|           |      | 0b1: Thermal monitoring is enabled. The thermal monitoring circuit on every Tper                                                  |

|           |      | period (if THMper is set) or when FrcTHM is set, and if necessary, turns off the boost                                            |

|           |      | converter to halt charging of the battery.                                                                                        |

|           |      | I <sup>2</sup> C Control of The WAKE Output                                                                                       |

| FrcWAKE   | 2    | OhO. WAVE subject to controlled by the WAVE community                                                                             |

|           |      | 0b0: WAKE output is controlled by the WAKE comparator.  0b1: WAKE output is high regardless of the status of the WAKE comparator. |

|           |      | Obt. WARL output is high regardless of the status of the WARL comparator.                                                         |

|           |      | I <sup>2</sup> C Control of Device Enable                                                                                         |

| DeviceEnb | 1    | OhO: Davies anable is controlled by the ENb pin                                                                                   |

|           |      | 0b0: Device enable is controlled by the ENb pin.                                                                                  |

|           |      | 0b1: Device disabled regardless of the status of the ENb pin.                                                                     |

|           |      | I <sup>2</sup> C Enable of the Boost Converter                                                                                    |

| BoostEnb  | 0    | 0b0: Boost converter is controlled by the internal digital logic.                                                                 |

|           |      | 0b1: Boost converter is disabled regardless of the internal digital logic.                                                        |

|           |      |                                                                                                                                   |

## VOCMeas (0x09)

| BIT         | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|-------------|---|---|---|---|---|---|

| Field       |   | VOC[7:0]    |   |   |   |   |   |   |

| Reset       |   | 0x1D        |   |   |   |   |   |   |

| Access Type |   | Write, Read |   |   |   |   |   |   |