# **User Manual**

# ITA-5730 Series

Intel<sup>®</sup> 3rd Generation Core<sup>™</sup> i Processor Fanless System for railway applications

## Copyright

The documentation and the software included with this product are copyrighted 2014 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

#### **Acknowledgements**

The ITA-5730 is trademark of Advantech Co., Ltd.

All other product names or trademarks are properties of their respective owners.

## **Product Warranty (2 years)**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandize authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

Part No. 200K573030 Printed in Taiwan Edition 1 May 2014

## **Technical Support and Assistance**

- 1. Visit the Advantech website at http://support.advantech.com where you can find the latest information about the product.

- Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

#### A Message to the Customer

#### **Advantech Customer Services**

Each and every Advantech product is built to the most exacting specifications to ensure reliable performance in the harsh and demanding conditions typical of industrial environments. Whether your new Advantech equipment is destined for the laboratory or the factory floor, you can be assured that your product will provide the reliability and ease of operation for which the name Advantech has come to be known. Your satisfaction is our primary concern. Here is a guide to Advantech's cus- tomer services.

To ensure you get the full benefit of our services, please follow the instructions below carefully.

#### **Technical Support**

We want you to get the best performance possible from your products. If you run into technical difficulties, we are here to help. For the most frequently asked questions, you can easily find answers in your product documentation. These answers are normally a lot more detailed than the ones we can give over the phone.

Please consult this manual first. If you still cannot find the answer, gather all the information or questions that apply to your problem, and with the p can be assured that your product will provide the reliability and ease of operation forfloor, you can be assured that your product will provide the reliability and ease of o oy oroduct close at hand, call your dealer. Our dealers are well trained and ready to give you the support you need to get the most from your Advantech products. In fact, most problems reported are minor and can be easily solved over the phone.

In addition, free technical support is available from Advantech engineers every business day. We are always ready to give advice about application requirements or specific information on the installation and operation of any of our products.

### **Initial Inspection**

Before setting up the system, check that the items listed below are included and in good condition. If any item does not accord with the table, please contact your dealer immediately.

- 1 x ITA-5730 series industrial computer

- 1 x ITA-5730 accessory box

- 1 x Warranty card

If any of these items are missing or damaged, contact your distributor or sales representative immediately. We have carefully inspected the ITA-5730 mechanically and electrically before shipment. It should be free of marks and scratches and in perfect working order upon receipt. As you unpack the ITA-5730, check it for signs of shipping damage. (For examples: box damage, scratches, dents, etc.) If it is damaged or it fails to meet the specifications, notify our service department or your local sales representative immediately. Also, please notify the carrier. Retain the shipping carton and packing material for inspection by the carrier. After inspection, we will make arrangements to repair or replace the unit.

## **Safety Instructions**

- Read these safety instructions carefully.

- 2. Keep this User Manual for later reference.

- 3. For plug-in equipment, the power outlet socket must be located near the equipment and must be easily accessible.

- 4. Keep this equipment away from humidity.

- 5. Put this equipment on a reliable surface during installation. Dropping it or letting it fall may cause damage.

- 6. The openings on the enclosure are for air convection. Protect the equipment from overheating. DO NOT COVER THE OPENINGS.

- 7. Make sure the voltage of the power source is correct before connecting the equipment to the power outlet.

- 8. Position the power cord so that people cannot step on it. Do not place anything over the power cord.

- 9. All cautions and warnings on the equipment should be noted.

- 10. If the equipment is not used for a long time, disconnect it from the power source to avoid damage by transient overvoltage.

- 11. Never pour any liquid into an opening. This may cause fire or electrical shock.

- 12. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

- 13. If one of the following situations arises, get the equipment checked by service personnel:

- The power cord or plug is damaged.

- Liquid has penetrated into the equipment.

- The equipment has been exposed to moisture.

- The equipment does not work well, or you cannot get it to work according to the user's manual.

- The equipment has been dropped and damaged.

- The equipment has obvious signs of breakage.

- 14. DO NOT LEAVE THIS EQUIPMENT IN AN ENVIRONMENT WHERE THE STORAGE TEMPERATURE MAY GO BELOW -40° C (-104° F) OR ABOVE 55° C (131° F). THIS COULD DAMAGE THE EQUIPMENT. THE EQUIPMENT SHOULD BE IN A CONTROLLED ENVIRONMENT.

- 15. CAUTION: DANGER OF EXPLOSION IF BATTERY IS INCORRECTLY REPLACED. REPLACE ONLY WITH THE SAME OR EQUIVALENT TYPE RECOMMENDED BY THE MANUFACTURER, DISCARD USED BATTERIES ACCORDING TO THE MANUFACTURER'S INSTRUCTIONS.

The sound pressure level at the operator's position according to IEC 704-1:1982 is no more than 70 dB (A).

DISCLAIMER: This set of instructions is given according to IEC 704-1. Advantech disclaims all responsibility for the accuracy of any statements contained herein.

# **Safety Precaution - Static Electricity**

Follow these simple precautions to protect yourself from harm and the products from damage.

- To avoid electrical shock, always disconnect the power from your PC chassis before you work on it. Don't touch any components on the CPU card or other cards while the PC is on.

- Disconnect power before making any configuration changes. The sudden rush of power as you connect a jumper or install a card may damage sensitive electronic components.

#### **Battery Information**

Batteries, battery packs and accumulators should not be disposed of as unsorted household waste. Please use the public collection system to return, recycle, or treat them in compliance with the local regulations.

## Warnings, Cautions and Notes

Warning! Warnings indicate conditions, which if not observed, can cause personal injury!

Caution! Cautions are included to help you avoid damaging hardware or losing data. e.g.

There is a danger of a new battery exploding if it is incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

Note! Notes provide optional additional information.

# **Contents**

| Chapter | 1   | Ove     | erview                                                  | 1        |

|---------|-----|---------|---------------------------------------------------------|----------|

|         | 1.1 | Introdu | iction                                                  | 2        |

|         | 1.2 |         | cations                                                 |          |

|         | 1.3 |         | Information                                             |          |

|         |     |         | Table 1.1: Power                                        |          |

|         | 1.4 | Enviro  | nmental Specifications                                  |          |

|         |     |         | Table 1.2: Environmental Specifications                 |          |

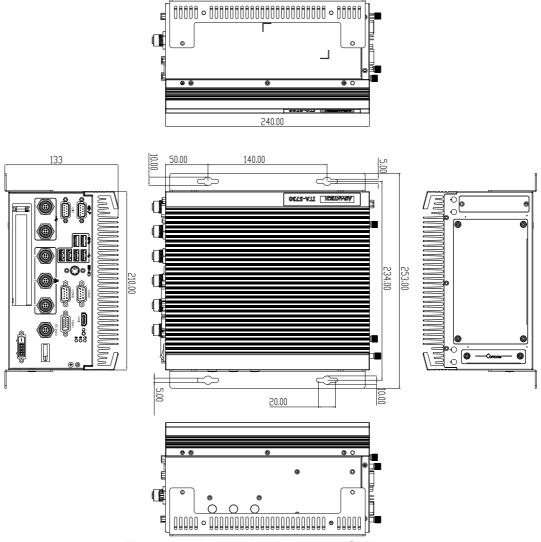

|         | 1.5 | Dimen   | sion Diagram                                            |          |

|         |     |         | Figure 1.1 Dimension Diagram of ITA-5730                |          |

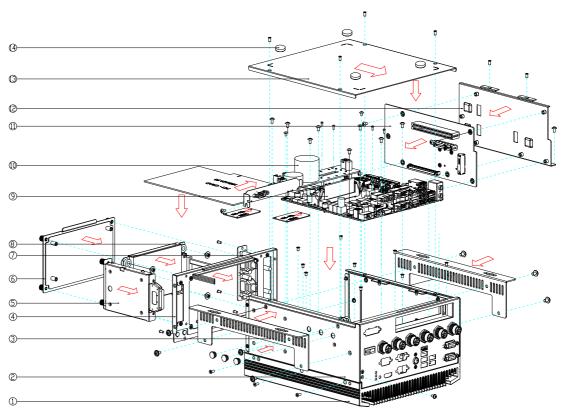

|         |     |         | Figure 1.2 Exploded Diagram of ITA-5730                 |          |

|         |     |         | Table 1.3: Part List                                    |          |

| Chapter | 2   | H/W     | / Installation                                          | 5        |

|         | 2.1 | Introdu | iction                                                  | 6        |

|         | 2.1 |         | rs and Connectors                                       |          |

|         | 2.2 | 2.2.1   | Jumper Description                                      |          |

|         |     | 2.2.2   | Jumper and Connector Location                           |          |

|         |     | 2.2.2   | Figure 2.1 Jumper and Connector Location on Main Board  |          |

|         |     |         | Table 2.1: Jumpers                                      |          |

|         |     |         | Table 2.2: JLVDS1: LVDS Voltage Selection               |          |

|         |     |         | Table 2.3: JCMOS1: CMOS Clear Function                  |          |

|         |     |         | Table 2.4: PSON1: Startup-up Mode Selection             |          |

|         |     |         | Table 2.5: VCCGPIO1: GPIO Voltage Selection             |          |

|         |     |         | Figure 2.2 Jumper and Connector Location on Riser Board |          |

|         | 2.3 | I/O Co  | nnectors                                                |          |

|         | 2.5 | 1/0 00  | Figure 2.3 ITA-5730 Rear I/O Interfaces                 |          |

|         |     |         | Figure 2.4 ITA-5730 Front I/O Interfaces                |          |

|         |     | 2.3.1   | COM Connector                                           |          |

|         |     | 2.0.1   | Table 2.6: COM Connector Pin Definition                 |          |

|         |     | 2.3.2   | HDMI Connector                                          |          |

|         |     | 2.5.2   | Table 2.7: HDMI Connector Pin Definition                |          |

|         |     | 2.3.3   | VGA Connector                                           |          |

|         |     | 2.5.5   | Table 2.8: VGA Connector Pin Definition                 |          |

|         |     | 2.3.4   | USB 2.0 Connector                                       |          |

|         |     | 2.3.4   | Table 2.9: USB2.0 Connector Pin Definition              | 12<br>12 |

|         |     | 2.3.5   | USB 3.0 Connector                                       |          |

|         |     | 2.3.3   | Table 2.10: USB3.0 Connector Pin Definition             |          |

|         |     | 2.3.6   | DIO Connector                                           |          |

|         |     | 2.3.0   | Table 2.11:DIO Connector Pin Definition                 |          |

|         |     | 2.3.7   | Audio in Connector                                      |          |

|         |     | 2.3.1   | Table 2.12: Audio Pin Definition                        |          |

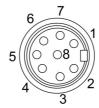

|         |     | 220     | PS/2 Connector                                          |          |

|         |     | 2.3.8   | Table 2.13: PS/2 Connector Pin Definition               |          |

|         |     | 220     |                                                         |          |

|         |     | 2.3.9   | LAN(M12, A-coded, 8-pin, Female)                        |          |

|         |     | 0 0 40  | Table 2.14: Ethernet Connector Pin Definition           |          |

|         |     | 2.3.10  | USB2.0(M12,A-coded,4-pin, Female)                       |          |

|         |     | 0.0.44  | Table 2.15: USB Connector Pin Definition                |          |

|         |     | 2.3.11  | Power Input(M12,A-coded,4-pin, Male)                    |          |

|         |     | 0.0.40  | Table 2.16: Power Connector Pin Definition              |          |

|         |     | 2.3.12  | LED Indicators for System Status                        | 15       |

| Chapter | 3   | System Setup                                                           | 17         |

|---------|-----|------------------------------------------------------------------------|------------|

|         | 3.1 | Introduction                                                           | 18         |

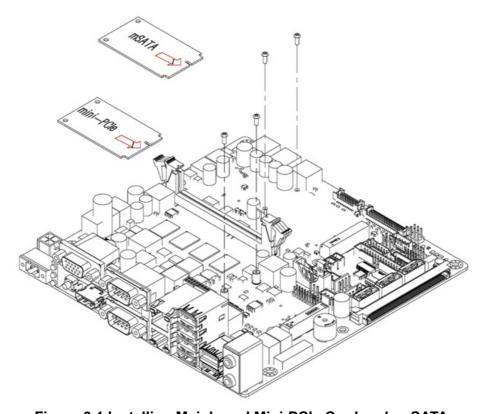

|         |     | 3.1.1 Installing Mainboard mini-PCle Card and m-SATA                   |            |

|         |     | Figure 3.1 Installing Mainboard Mini-PCle Card and m-SATA              | ۱ 18       |

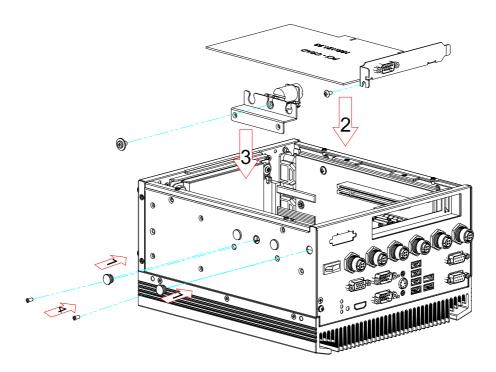

|         |     | 3.1.2 Installing PCI card                                              |            |

|         |     | Figure 3.2 Installing PCI Card                                         |            |

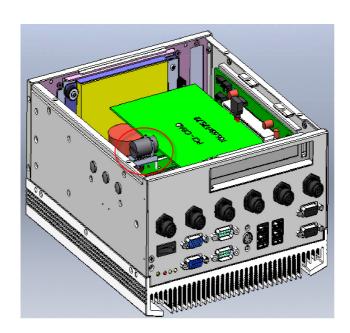

|         |     | 3.1.3 Installing HDD Module and Easy-swap CF Module                    |            |

|         |     | Figure 3.3 Installing CF Module                                        |            |

|         |     | Figure 3.4 Installing HDD Module                                       |            |

|         |     | 3.1.4 Installing Top Cover                                             |            |

|         |     | Figure 3.5 Installing Top Cover                                        |            |

|         |     | 3.1.5 Installing Foot Stand                                            |            |

|         |     | Figure 3.6 Installing Foot Stand                                       |            |

|         |     | Figure 3.7 Desktop Mount                                               |            |

|         |     | Figure 3.8 Wall Mount                                                  |            |

|         |     | rigure 5.6 Waii Wourit                                                 | 20         |

| Chapter | 4   | BIOS Setting                                                           | 27         |

|         | 4.1 | Introduction                                                           | 28         |

|         | ••• | Figure 4.1: Setup Program Initial Screen                               |            |

|         | 4.2 | Entering Setup                                                         |            |

|         |     | Figure 4.2: POST Screen                                                |            |

|         |     | 4.2.1 Main Setup                                                       |            |

|         |     | Figure 4.3: Main Setup Screen                                          |            |

|         |     | 4.2.2 Advanced BIOS Features Setup                                     |            |

|         |     | Figure 4.4: Advanced BIOS Features Setup Screen                        |            |

|         |     | Figure 4.5 ACPI Configuration                                          |            |

|         |     | Figure 4.6: CPU Configuration (1)                                      |            |

|         |     | Figure 4.7 CPU Configuration (2)                                       |            |

|         |     | Figure 4.8 SATA Configuration                                          |            |

|         |     | Figure 4.9: USB Configuration                                          |            |

|         |     | Figure 4.10:Super I/O Configuration                                    |            |

|         |     | Figure 4.11Serial Port Configuration                                   |            |

|         |     | Figure 4.12:H/W Monitor COnfigurationFigure 4.13:CPU PPM Configuration |            |

|         |     | Figure 4.14:APM Configuration                                          |            |

|         |     | 4.2.3 Advanced Chipset Features Setup                                  |            |

|         |     | Figure 4.15Advanced Chipset Features Setup                             |            |

|         |     | Figure 4.16PCH-IO Configuration                                        |            |

|         |     | Figure 4.17Chipset USB Configuration                                   |            |

|         |     | Figure 4.18PCH Azalia Configuration                                    |            |

|         |     | Figure 4.19:System Agent (SA) Configuration                            |            |

|         |     | Figure 4.20 Graphics Configuration Menu                                |            |

|         |     | Figure 4.21LCD Control                                                 |            |

|         |     | 4.2.4 Boot Setup                                                       | 42         |

|         |     | Figure 4.22:Boot Setup                                                 |            |

|         |     | Figure 4.23Boot Option Priorities                                      |            |

|         |     | Figure 4.24:CSM Parameter                                              |            |

|         |     | 4.2.5 Security Setup                                                   |            |

|         |     | Figure 4.25:Setup Security Menu                                        |            |

|         |     | 4.2.6 Save & Exit Setup                                                |            |

|         |     | Figure 4.26:Setup Save & Exit Menu                                     | 45         |

| Chapter | 5   | Driver Installation                                                    | <b>4</b> 7 |

| Julytoi |     |                                                                        |            |

|         | 5 1 | Introduction                                                           | 48         |

|         | 5.2 | Driver Installation                     | 48   |

|---------|-----|-----------------------------------------|------|

|         |     | 5.2.1 Chipset Windows Driver Setup      | 49   |

|         |     | 5.2.2 VGA Windows Driver Setup          | 49   |

|         |     | 5.2.3 ME Windows Driver Setup           | 50   |

|         |     | 5.2.4 LAN Windows Driver Setup          |      |

|         |     | 5.2.5 USB 3.0 Windows Driver Setup      | 51   |

|         |     | 5.2.6 Audio Windows Driver Installation | 51   |

| Chapter | 6   | GPIO Programming Guide                  | 53   |

|         | 6.1 | ITA-5730 Digital DIO Definition         | 54   |

|         | 6.2 | Configuration Sequence                  |      |

|         | 6.3 | Function Call for Reference             |      |

| Appendi | хА  | Programming the Watchdog Tim            | er63 |

|         | A.1 | Programming the Watchdog Timer          | 64   |

|         |     | A.1.1 Watchdog Timer Overview           | 64   |

|         |     | A.1.2 Programming the Watchdog Timer    |      |

|         |     | Table A.1: Watchdog Timer Registers     | 64   |

|         |     | A.1.3 Example Program                   | 65   |

# Chapter

# Overview

**Sections include:**

- Introduction

- **■** Specifications

- **■** Power Information

- **■** Environment Specifications

- Dimension Diagram

#### 1.1 Introduction

The ITA-5730 is a fanless, compact embedded industrial computer chassis with Core<sup>TM</sup> i7/i5/i3 dual core processor and wide voltage input range, which is specially designed for intelligent transportation - Road Surveillance. This powerful computing platform can stand operation 24 hours a day, 7 days a week.

#### 1.2 Specifications

- **Processor and Chipset:** Core<sup>TM</sup> i7/i5/i3 processor + Intel® HM76 chipset

- BIOS: AMI SPI 64 Mb Flash

- Memory: On-board 4 GB DDR3 1333/1600 MHz

- **Display:** Integrated graphics HD4000, with up to 256 MB SDRAM shared system memory

- Dual Display:

- Single display resolution up to 2048 x 1536 @ 60 Hz

- Dual Display resolution up to 1920 x 1200 @ 60 Hz

- Storage: Supports 1 x 2.5" SSD Tray, 1 x Easy-swap CF Tray, 1 x mSATA socket on board

- Expansion Slot: 2 x Mini PCle slot, 1 x SIM card slot, 1 x PCl slot

- Ethernet: 3 x 10/100/1000M Ethernet, M12 A-coded(F) 8-pin (Controller chip: Intel i210-IT)

- USB:

- 2 x USB2.0 with M12 A-coded(F) 4-pin

- 4 x USB2.0 with Type A

- 2 x USB3.0 with Type A

- VGA: 1 x VGA

- **HDMI**:1 x HDMI

- Serial I/O: 2 x DB9, RS232/422/485 with automatic flow control

- **Digital I/O:** 1 x 8-ch GPIO

- **Audio:** 1 x Speaker out with 2 x 4 w amplifer,1 Mic input; DB9 type

- Reserved Zone: 1 x PCI expansion slot (Real I/O panel)

- Dimensions (W x H x D):

- 210 x 129 x 240 mm (without ears)

- 253 x 133 x 240 mm (with ears)

- Weight: 3.75 kg

#### 1.3 Power Information

ITA-5730 supports 24V/48V/72V/110V DC voltage input compliant with EN 50155.

| Table 1.1: Power   |                           |      |      |       |  |

|--------------------|---------------------------|------|------|-------|--|

| DC voltage input   | 24 V                      | 48 V | 72 V | 110 V |  |

| DC power interface | e M12 A-coded(Male) 4-pin |      |      |       |  |

# 1.4 Environmental Specifications

| Table 1.2: Environmental Specifications |                                                                 |  |  |

|-----------------------------------------|-----------------------------------------------------------------|--|--|

| <b>Operating Temperature</b>            | EN50155 T2 level: -40 ~ 55°C (with industrial storage)          |  |  |

| Safety Certificate<br>Temperature       | -10 ~ 50°C (With industrial standard SSD/CF/mSATA)              |  |  |

| Storage Temperature                     | -40 ~ 85°C                                                      |  |  |

| Humidity                                | 95% @ 40° C, non-condensing                                     |  |  |

|                                         | With Compact Flash: 2 Grms @ 5 ~ 500 Hz, random, 1 hr/axis      |  |  |

| Vibration                               | With 2.5" HDD: 0.5 Grms @ 5 ~ 500 Hz, random, 1 hr/axis         |  |  |

|                                         | IEC60068-2-6 Sine 2G @ 5 ~ 500Hz, 1hr/axis                      |  |  |

|                                         | With Compact Flash: 20G, IEC-68-2-27, half-sine wave, 11 ms     |  |  |

| Shock                                   | duration                                                        |  |  |

|                                         | With 2.5" HDD: 10G, IEC-68-2-27, half-sine wave, 11 ms duration |  |  |

| Safety                                  | UL, CCC, BSMI, CE and FCC compliant                             |  |  |

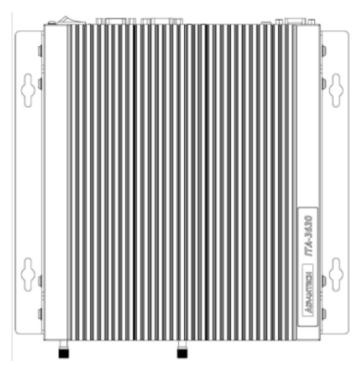

# 1.5 **Dimension Diagram**

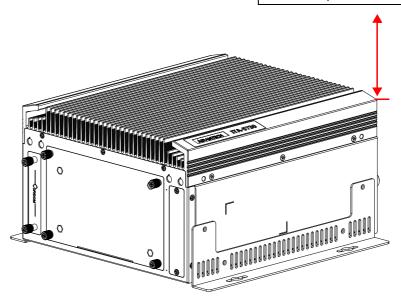

Figure 1.1 Dimension Diagram of ITA-5730

Figure 1.2 Exploded Diagram of ITA-5730

| Table 1.3: Part List |                    |    |                       |  |

|----------------------|--------------------|----|-----------------------|--|

| 1                    | Heat sink          | 8  | SSD support bracket   |  |

| 2                    | Chassis            | 9  | Main Board            |  |

| 3                    | Chassis foot stand | 10 | Power Board           |  |

| 4                    | SSD bracket        | 11 | Riser Board           |  |

| 5                    | CF Tray            | 12 | Riser support bracket |  |

| 6                    | SSD Door           | 13 | Top Cover             |  |

| 7                    | Blank bracket      | 14 | Rubber foot pad       |  |

|                      |                    | •  | •                     |  |

# Chapter

# H/W Installation

Sections include:

- Introduction

- **■** Jumpers and Connectors

- I/O Connectors

#### 2.1 Introduction

The following sections show the internal jumpers setting and the external connectors pin assignment for application integration.

## 2.2 Jumpers and Connectors

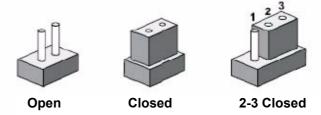

#### 2.2.1 Jumper Description

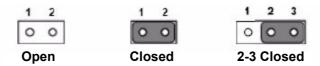

You may configure the ITA-5730 to match the needs of your application by setting jumpers. A jumper is a metal bridge used to close an electric circuit. It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To close a jumper, you remove the clip. Sometime a jumper will have three pins, labelled 1, 2 and 3. In this case you would connect either pins 1 and 2, or 2 and 3.

The jumpers setting are schematically depicted in this manual as follows.

A pair of needle-nose pliers may be helpful when working with jumpers. If you have any doubts about the best hardware configuration for your application, contact your local distributor or sales representative before you make any changes. Generally, you simply need a standard cable to make most connections.

#### 2.2.2 Jumper and Connector Location

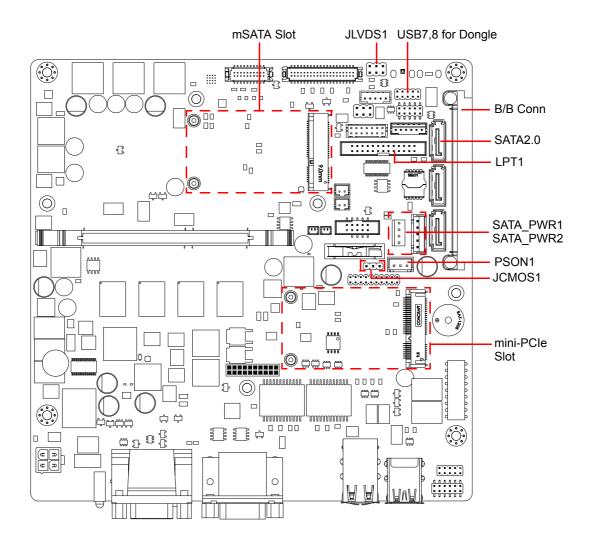

The board has a number of connectors and jumpers that allow you to configure your system to suit your application. The table below lists the function of each of the connectors and jumpers. The locations of jumpers and connector on the board are shown in Figure 2.1.

Figure 2.1 Jumper and Connector Location on Main Board

| Table 2.1: Jumpers |                         |  |  |

|--------------------|-------------------------|--|--|

| Label              | Function                |  |  |

| JLVDS1             | LVDS voltage selection  |  |  |

| JCMOS1             | Clear CMOS settings     |  |  |

| PSON1              | Start-up mode selection |  |  |

| VCCGPIO1           | GPIO voltage selection  |  |  |

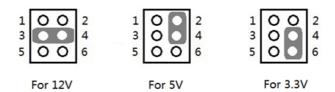

| Table 2.2: JLVDS1: LVDS Voltage Selection |                 |  |

|-------------------------------------------|-----------------|--|

| Closed Pins                               | Setting         |  |

| 3-4<br>2-4                                | +V12            |  |

| 2-4                                       | +V5             |  |

| 4-6                                       | Normal (+V3.3)* |  |

| *Default setting                          |                 |  |

| Table 2.3: JCMOS1: CMOS Clear Function |            |  |  |  |

|----------------------------------------|------------|--|--|--|

| Closed Pins                            | Setting    |  |  |  |

| 1-2                                    | Default*   |  |  |  |

| 2-3                                    | Clear CMOS |  |  |  |

| * Default setting                      |            |  |  |  |

| Closed Pins       | Setting   |       |  |  |

|-------------------|-----------|-------|--|--|

| 1-2               | AT Mode   |       |  |  |

| 2-3               | ATX Mode* |       |  |  |

| * Default setting |           |       |  |  |

|                   | 1 2 3     | 1 2 3 |  |  |

| Table 2.5: VCCGPIO1: GPIO Voltage Selection |                    |  |  |

|---------------------------------------------|--------------------|--|--|

| Closed Pins                                 | Setting            |  |  |

| 1-3                                         | +V5_SB             |  |  |

| 2-4                                         | Normal (+V3.3_SB)* |  |  |

| 3-5<br>4-6                                  | +V5                |  |  |

| 4-6                                         | +V3.3              |  |  |

| * Default setting                           |                    |  |  |

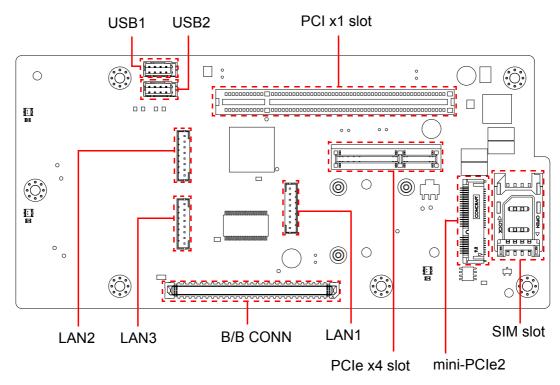

Figure 2.2 Jumper and Connector Location on Riser Board

## 2.3 I/O Connectors

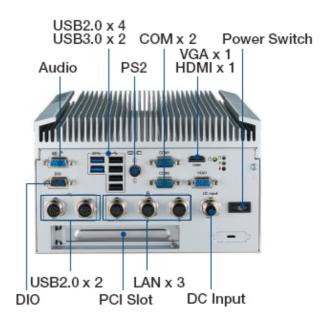

Figure 2.3 ITA-5730 Rear I/O Interfaces

Figure 2.4 ITA-5730 Front I/O Interfaces

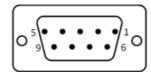

#### 2.3.1 COM Connector

ITA-5730 provides two D-sub 9-pin connectors for RS-232/422/485. The default setting is RS-232.

| Table 2.6: COM Connector Pin Definition |             |             |             |  |

|-----------------------------------------|-------------|-------------|-------------|--|

|                                         | RS-232      | RS-422      | RS-485      |  |

| Pin                                     | Signal Name | Signal Name | Signal Name |  |

| 1                                       | DCD         | Tx-         | DATA-       |  |

| 2                                       | RxD         | Tx+         | DATA+       |  |

| 3                                       | TxD         | Rx+         | NC          |  |

| 4                                       | DTR         | Rx-         | NC          |  |

| 5                                       | GND         | GND         | GND         |  |

| 6                                       | DSR         | NC          | NC          |  |

| 7                                       | RTS         | NC          | NC          |  |

| 8                                       | CTS         | NC          | NC          |  |

| 9                                       | RI          | NC          | NC          |  |

#### 2.3.2 HDMI Connector

| Table 2 | Table 2.7: HDMI Connector Pin Definition |          |                   |  |

|---------|------------------------------------------|----------|-------------------|--|

| Pin     | Signal Name                              | Signal N | ame Signal Name   |  |

| 1       | TMDS Data2+                              | 11       | TMDS Clock Shiled |  |

| 2       | TMDS Data2 Shiled                        | 12       | TMDS Clock-       |  |

| 3       | TMDS Data2-                              | 13       | Reserved          |  |

| 4       | TMDS Data1+                              | 14       | Reserved          |  |

| 5       | TMDS Data1 Shiled                        | 15       | SCL               |  |

| 6       | TMDS Data1-                              | 16       | SDA               |  |

| 7       | TMDS Data0+                              | 17       | DDC/CEC Ground    |  |

| 8       | TMDS Data0 Shiled                        | 18       | +5V Power         |  |

| 9       | TMDS Data0-                              | 19       | Hot Plug Detect   |  |

| 10      | TMDS Clock+                              |          |                   |  |

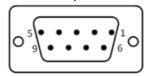

#### 2.3.3 VGA Connector

ITA-5730 offers one D-sub 15-pin female connector, which supports max. resolution of 2048 x 1563.

| Table | Table 2.8: VGA Connector Pin Definition |     |             |  |  |

|-------|-----------------------------------------|-----|-------------|--|--|

| Pin   | Signal Name                             | Pin | Signal Name |  |  |

| 1     | Red                                     | 9   | +5V         |  |  |

| 2     | Green                                   | 10  | GND         |  |  |

| 3     | Blue                                    | 11  | NC          |  |  |

| 4     | NC                                      | 12  | DDC-DATA    |  |  |

| 5     | GND                                     | 13  | H-SYNC      |  |  |

| 6     | GND                                     | 14  | V-SYNC      |  |  |

| 7     | GND                                     | 15  | DDC-CLK     |  |  |

| 8     | GND                                     |     |             |  |  |

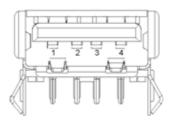

#### 2.3.4 USB 2.0 Connector

ITA-5730 provides four USB interface connectors, which are USB EHCI, Rev. 2.0 compliant. The USB interface can be disabled in the system BIOS setup.

| Table 2.9: USB2.0 Connector Pin Definition |             |     |             |  |

|--------------------------------------------|-------------|-----|-------------|--|

| Pin                                        | Signal Name | Pin | Signal Name |  |

| 1                                          | +V5(VCC)    | 3   | USB DATA+   |  |

| 2                                          | USB DATA-   | 4   | GND         |  |

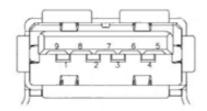

#### 2.3.5 USB 3.0 Connector

ITA-5730 provides two USB interface connectors, which are USB XHCI, Rev. 3.0 compliant. The USB interface can be disabled in the system BIOS setup.

| Table 2.10: USB3.0 Connector Pin Definition |             |     |             |

|---------------------------------------------|-------------|-----|-------------|

| Pin                                         | Signal Name | Pin | Signal Name |

| 1                                           | +V5(VCC)    | 6   | StdA_SSRX+  |

| 2                                           | D-          | 7   | GND_DRAIN   |

| 3                                           | D+          | 8   | StdA_SSTX-  |

| 4                                           | GND         | 9   | StdA_SSTX+  |

| 5                                           | StdA_SSRX-  |     |             |

#### 2.3.6 DIO Connector

ITA-5730 provides one 8-bit DIO, D-sub 9-pin male connector without isolation protection.

| Table 2.11: DIO Connector Pin Definition |             |     |             |

|------------------------------------------|-------------|-----|-------------|

| Pin                                      | Signal Name | Pin | Signal Name |

| 1                                        | GPIO0       | 6   | GPIO4       |

| 2                                        | GPIO1       | 7   | GPIO5       |

| 3                                        | GPIO2       | 8   | GPIO6       |

| 4                                        | GPIO3       | 9   | GPIO7       |

| 5                                        | GND         |     |             |

#### 2.3.7 Audio in Connector

ITA-5730 provides one integrated Mic-in/speaker out audio connector with DB9 type.

| Table 2.12: Audio Pin Definition |             |     |             |

|----------------------------------|-------------|-----|-------------|

| Pin                              | Signal Name | Pin | Signal Name |

| 1                                | MIC1R       | 6   | LOUTR       |

| 2                                | GND_AUD     | 7   | GND_AUD     |

| 3                                | GND_AUD     | 8   | FRONT_JD    |

| 4                                | MIC_JD      | 9   | LOUTL       |

| 5                                | MIC1L       |     |             |

#### 2.3.8 PS/2 Connector

ITA-5730 provides a PS/2 keyboard and mouse connector.

| Table 2.13: PS/2 Connector Pin Definition |             |     |             |

|-------------------------------------------|-------------|-----|-------------|

| Pin                                       | Signal Name | Pin | Signal Name |

| 1                                         | KB_Z_DAT    | 4   | +V5_PS2     |

| 2                                         | MS_Z_DAT    | 5   | KB_Z_CLK    |

| 3                                         | GND         | 6   | MS_Z_CLK    |

#### 2.3.9 LAN(M12, A-coded, 8-pin, Female)

ITA-5730 provides 3 10/100/1000M Ethernet with M12 A-coded.

| Table 2.14: Ethernet Connector Pin Definition |             |  |  |

|-----------------------------------------------|-------------|--|--|

| Pin                                           | Signal Name |  |  |

| 1                                             | MDI2+       |  |  |

| 2                                             | MDI3+       |  |  |

| 3                                             | MDI3-       |  |  |

| 4                                             | MDI0-       |  |  |

| 5                                             | MDI1+       |  |  |

| 6                                             | MDI0+       |  |  |

| 7                                             | MDI2-       |  |  |

| 8                                             | MDI1-       |  |  |

## **2.3.10 USB2.0(M12,A-coded,4-pin, Female)**

| Table 2.15: USB Connector Pin Definition |             |  |  |

|------------------------------------------|-------------|--|--|

| Pin                                      | Signal Name |  |  |

| 1                                        | D-          |  |  |

| 2                                        | 5V          |  |  |

| 3                                        | D+          |  |  |

| 4                                        | GND         |  |  |

#### 2.3.11 Power Input(M12,A-coded,4-pin, Male)

ITA-5730 provides 24V/48V/72V/110V DC voltage input.

| Table 2.16: Power Connector Pin Definition |             |  |  |

|--------------------------------------------|-------------|--|--|

| Pin                                        | Signal Name |  |  |

| 1                                          | GND         |  |  |

| 2                                          | Power       |  |  |

| 3                                          | Power       |  |  |

| 4                                          | GND         |  |  |

#### 2.3.12 LED Indicators for System Status

LEDs on the rear panel are used to indicate system health and avtive status. For detailed information of LED definition, please refer to below table.

| Item | LED   | Status | Color  | Description                                          |

|------|-------|--------|--------|------------------------------------------------------|

| 1    | D\\/D | On     | Green  | System power is on and system is safe.               |

| ı    | FVVI  |        |        |                                                      |

| 2    | HDD   | On     | Yellow | There is data receiving and transmitting on SATA.    |

|      |       | Off    |        | There is no data receiving and transmitting on SATA. |

# Chapter

3

# **System Setup**

**Sections include:**

- Installing Mainboard mini-PCle card and mini SATA

- Installing USB Dongle

- Installing HDD Module

- Installing Foot Stand

- Installing Notes

## 3.1 Introduction

The following procedures will instruct you to install all modules into the ITA-5730 system.

#### 3.1.1 Installing Mainboard mini-PCle Card and m-SATA

- 1. ITA-5730 mainboard has a Mini PCIe slot and a m-SATA slot. Each one has a label for users to distinguish.

- 2. Insert mini-PCIe card and mSATA card to the respective slot and fix with two screws.

- 3. ITA-5730 also has a Mini PCle on Riser board, just refer step 1 to assemble.

Figure 3.1 Installing Mainboard Mini-PCle Card and m-SATA

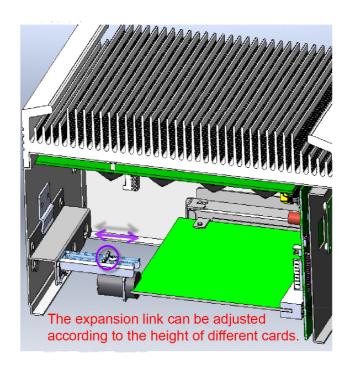

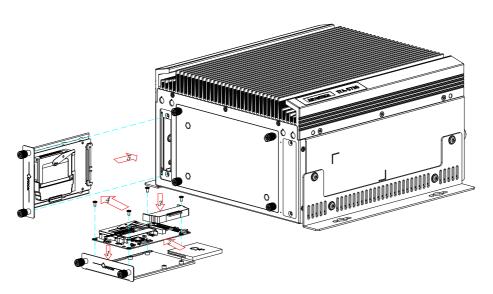

#### 3.1.2 Installing PCI card

ITA-5730 provides 1 PCI slot for customized expansion.

- 1. Remove screws from outside of the chassis.

- 2. Assemble I/O bracket with PCI card.

- 3. Assemble rubber to the expansion link and fix to PCI card together.

- 4. Tighten the step3 from the outside.

Figure 3.2 Installing PCI Card

#### Design the PCI interface card expansion link.

Inside view

2. Side view

3. After the PCI interface card is installed, the user can attach the expansion link to the side of the card (as shown in image below).

# Adjust the position of expansion link according to different height of PCI interface cards.

1. For 60~100 mm expansion cards:

2. For 100~122 mm expansion cards:

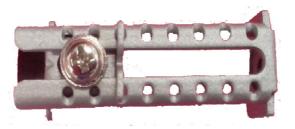

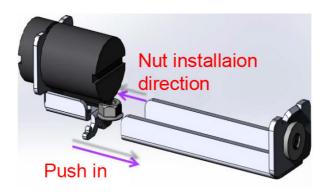

#### Adjust the expansion link.

Rubber installation direction (the length can be adjusted according to the height of card)

#### 2. Assembly direction

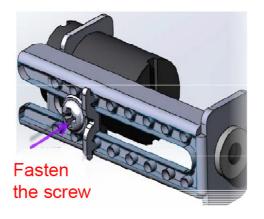

#### 3. Fasten the screw

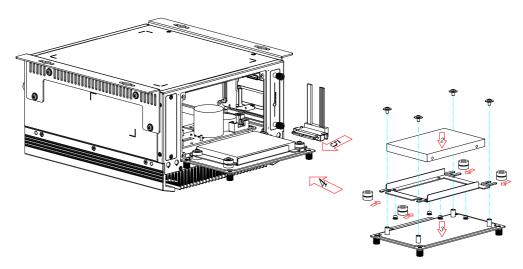

#### 3.1.3 Installing HDD Module and Easy-swap CF Module

The ITA-5730 reserves a space for 2.5" HDD module and CF module. And its design is benefit for customers to assemble or disassemble storage without tools.

- 1. Place the HDD into 2.5" HDD holder and fill in 4 rubbers.

- 2. Place two HDDs onto HDD holder, and secure them with 8 screws, then sitck the cooling pad.

- 3. Place HDD holder onto HDD bracket and secure it with 4 screws.

- 4. Connect the complete HDD module to the chassis and fix it with screws.

#### 3.1.3.1 Installing CF Module

- 1. Fix CF module board onto CF tray.

- 2. Insert the CF card into CF module board and fix it with fixed plastic shell.

- 3. Place CF tray onto HDD bracket and secure it with the screws.

- 4. Insert the CF module.

Figure 3.3 Installing CF Module

#### 3.1.3.2 Installing HDD Module

- Fix 4 rubbers to HDD bracket.

- 2. Place 2.5" HDD into HDD bracket and tighten with screws.

- 3. Assemble HDD bracket to HDD door.

- 4. Connect HDD to SATA cable.

- 5. Tighten up HDD door on chassis with hand locking screw.

Figure 3.4 Installing HDD Module

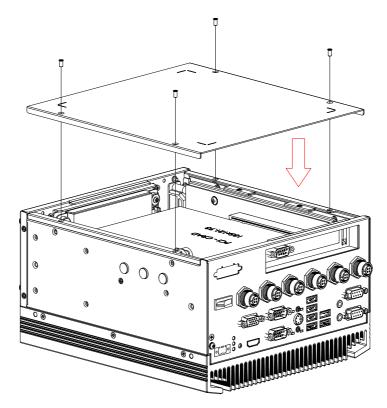

## 3.1.4 Installing Top Cover

Tighten up Top Cover to Chassis with 4 screws in four corners.

Figure 3.5 Installing Top Cover

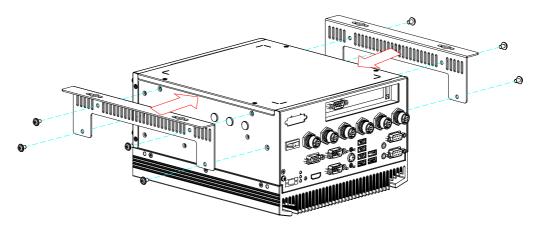

#### 3.1.5 Installing Foot Stand

Align the 2 foot stands with the screw holes in the chassis side panel, and secure them with screws.

Figure 3.6 Installing Foot Stand

#### 3.1.6 Installation Notes

When the computer is running, no object should be placed within 30 mm above the heatsink to avoid the impact on airflow.

To ensure an effective cooling during operation, no object should be placed within 30 mm above the heatsink to avoid the impact on airflow.

**Figure 3.7 Desktop Mount**

Figure 3.8 Wall Mount

Chapter

4

**BIOS Setting**

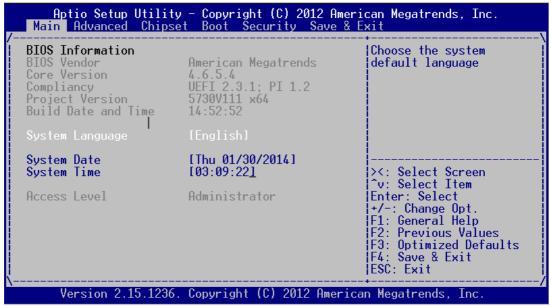

## 4.1 Introduction

This chapter introduces how to configure BIOS for ITA-5730 series. With the AMI-BIOS Setup program, you can modify BIOS settings and control the special features of your computer. The Setup program uses a number of menus forsaking changes and turning the special features on or off. This chapter describes the basic navigation of the ITA-5730 setup screens.

Figure 4.1: Setup Program Initial Screen

AMI's BIOS ROM has a built-in Setup program that allows users to modify the basic system configuration. This type of information is stored in BIOS ROM so it retains the Setup information when the power is turned off.

# 4.2 Entering Setup

Turn on the computer to enter POST screen, and BIOS and CPU information will be shown.press <DEL> and you will immediately be allowed to enter Setup.

```

Version 2.15.1236. Copyright (C) 2012 American Megatrends, Inc.

**** ITA-5730 BIOS V1.11 (02/13/2014) ****

Press <DEL> or <ESC> to enter setup.

-

```

Figure 4.2: POST Screen

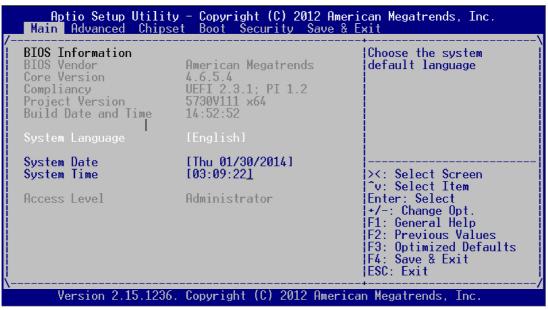

#### 4.2.1 Main Setup

When you first enter the BIOS Setup Utility, you will enter the Main setup screen. You can always return to the Main setup screen by selecting the Main tab. There are two Main Setup options. They are described in this section. The Main BIOS Setup screen is shown below.

Figure 4.3: Main Setup Screen

The Main BIOS setup screen has two main frames. The left frame displays all the options that can be configured. Graved-out options cannot be configured; options in blue can. The right frame displays the key legend.

Above the key legend is an area reserved for a text message. When an option is selected in the left frame, it is highlighted in white. Often a text message will accompany it.

#### **System Time / System Date**

Use this option to change the system time and date. Highlight System Time or System Date using the <Arrow> keys. Enter new values through the keyboard. Press the <Tab> key or the <Arrow> keys to move between fields. The date must be entered in MM/DD/YY format. The time must be entered in HH:MM:SS format.

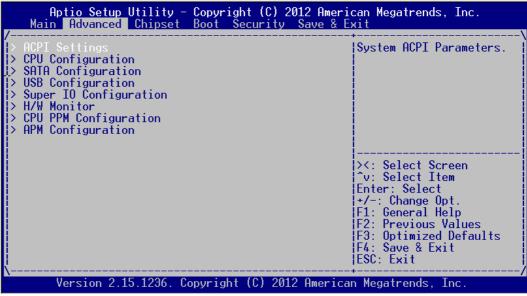

#### 4.2.2 Advanced BIOS Features Setup

Select the Advanced tab from the ITA-5730 setup screen to enter the Advanced BIOS Setup screen. You can select any of the items in the left frame of the screen, such as CPU Configuration, to go to the sub menu for that item. You can display an Advanced BIOS Setup option by highlighting it using the <Arrow> keys. All Advanced BIOS Setup options are described in this section. The Advanced BIOS Setup screen is shown below. The sub menus are described on the following pages.

Figure 4.4: Advanced BIOS Features Setup Screen

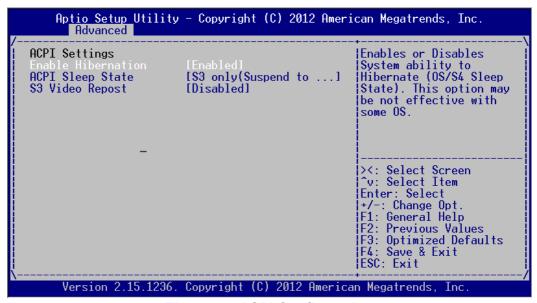

#### 4.2.2.1 **ACPI Configuration**

Figure 4.5 ACPI Configuration

#### Enable Hibernation

This item allows users to enable or disable Hibernation.

#### ACPI Sleep State

This item allows users to select APCI state during system hibernation.

#### S3 Video Repost

This item is used to decide whether to call VBIOS when the system resumes from S3/SRT. The default setting is "Disabled".

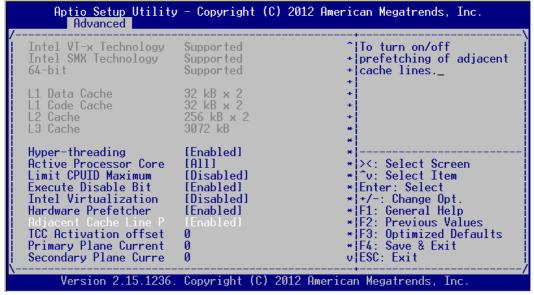

#### 4.2.2.2 CPU Configuration

| CPU Configuration  Intel(R) Core(TM) i5-3610ME CPU @ 2.70GHz CPU Signature 306a9 Microcode Patch 16 Max CPU Speed 2700 MHz Min CPU Speed 1200 MHz CPU Speed 2700 MHz Processor Cores 2 Intel HT Technology Supported Intel VI-x Technology Supported | Enabled for Windows XP                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel SMX Technology Supported Supported  L1 Data Cache 32 kB x 2 L1 Code Cache 32 kB x 2 L2 Cache 256 kB x 2 L3 Cache 3072 kB                                                                                                                       | * ^v: Select Item + Enter: Select + +/-: Change Opt. + F1: General Help + F2: Previous Values + F3: Optimized Defaults + F4: Save & Exit v ESC: Exit |

Figure 4.6: CPU Configuration (1)

Figure 4.7 CPU Configuration (2)

#### Hyper Threading

This item allows users to enable or disable Intel Hyper Threading Technology. The default setting is "Enabled".

#### Active Processor Core

This item allows users to choose how many processor cores to activate when you are using a dual or quad cores processor. The default setting is "All".

#### **■** Limit CPUID Maximum

This item allows users to set the limit value for CPUID. The default setting is "Disabled".

#### **■** Execute Disable Bit

This item is a hardware feature introduced by Intel in its new generation CPU. It can help CPU realize self-protection under the circumstance of hostile attack based on buffer overflow, so as to avoid the virus attack, such as blasting wave. The default setting is "Enabled".

#### Hardware Prefectcher

This item allows users to enable or disable Hardware Prefecther Technology. The default setting is "Enabled".

#### Adjacent Cache Line Prefetch

This item allows users to enable or disable sequential access to memory. The default setting is "Enabled".

#### Intel Virtualization Technology

This item is a system virtualization technology adopted in CPU produced by Intel. It allows multiple operating systems to run simultaneously on the same system. It adopts Vanderpool Technology, which allows multiple systems to run on the same system and applications can run in their own individual space. The default setting is "Enabled".

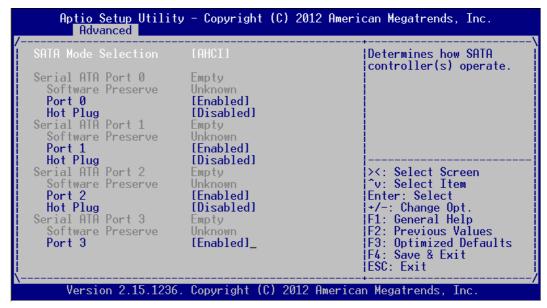

#### 4.2.2.3 SATA Configuration

Figure 4.8 SATA Configuration

#### SATA Mode Selection

This item allows users to select configuration mode of SATA Controller(s). The default setting is "AHCI".

#### 4.2.2.4 USB Configuration

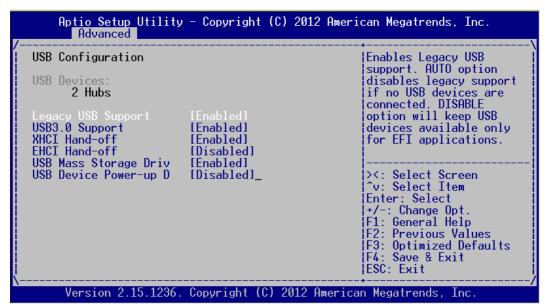

Figure 4.9: USB Configuration

#### Legacy USB Support

This item allows users to enable support for traditional USB. It will be automatically set as "Disabled" when no USB device is connected. The default setting is "Enabled".

#### ■ USB 3.0 Support

This item allows users to enable or disable USB 3.0 (XHCI). The default setting is "Enabled".

#### XHCI Hand-off

This item is to enable or disable function of supporting OS without XHCI Handoff feature. The default setting is "Enabled".

#### **■** EHCl Hand-off

This item is to enable or disable function of supporting OS without EHCI Handoff feature. The default setting is "Disabled".

#### ■ USB Mass Storage Driver Support

This item allows users to set the specific type of the connected USB device.

#### USB Device Power-up Delay

This item allows users to enable or disable the function of USB device reporting max. delay time to host controller. The default setting is "Disabled".

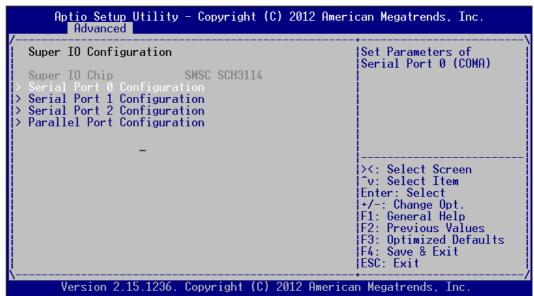

#### 4.2.2.5 Super I/O Configuration

Figure 4.10: Super I/O Configuration

Figure 4.11 Serial Port Configuration

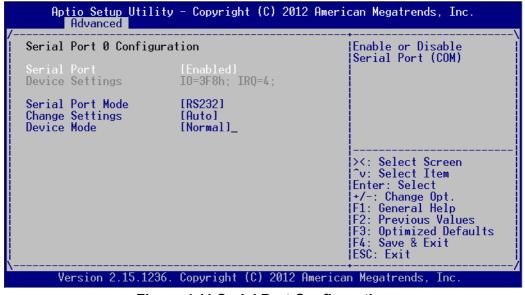

#### **Serial Port 0 Configuration**

#### Serial Port

This item allows users to open or close serial port. The default setting is "Enabled".

#### Serial Port Mode

This item allows users to set serial port as RS232/422/485. The default setting is "RS232".

#### Change Settings

IO=3F8h; IRQ=4;

IO=3F8h; IRQ=3,4,5,6,7,10,11,12;

This item allows users to select IO address and IRQ to change serial port settings.

#### **Device Mode**

This item allow users to select device mode. The default setting is "Normal Mode".

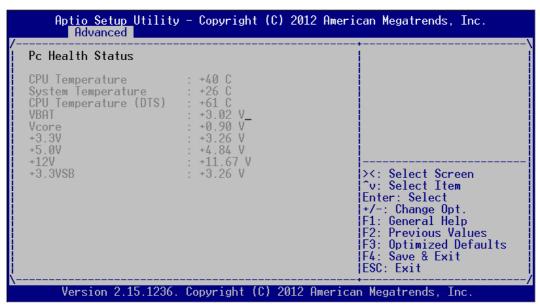

#### 4.2.2.6 **H/W Monitor**

Figure 4.12: H/W Monitor COnfiguration

#### **PC Health Status**

This item is used to hardware safety detection. BIOS will display the current system temperature, CPU temperature and other related voltage values. All these parameters have a certain range, so operations out of the range should be avoided.

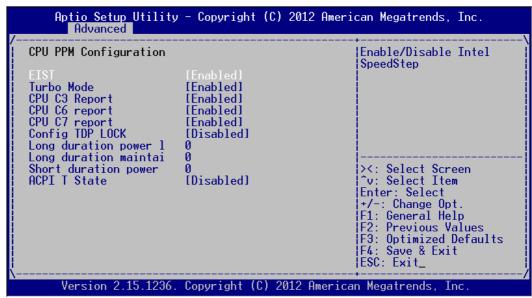

#### 4.2.2.7 CPU PPM Configuration

Figure 4.13: CPU PPM Configuration

#### EIST

This item is used to set CPU SpeedStep function. The default setting is "Enabled".

#### Turbo Mode

This item is used to set CPU Turbo mode function. The default setting is "Enabled".

#### ■ CPU C3/C6/7 Report

This item is used to set CPU C-state function. The default setting is "Enabled".

#### ■ Config TDP LOCK

This item is used to set Config TDP LOCK function. The default setting is "Disabled".

#### ACPI T State

This item is used to set ACPI T State function. The default setting is "Disabled".

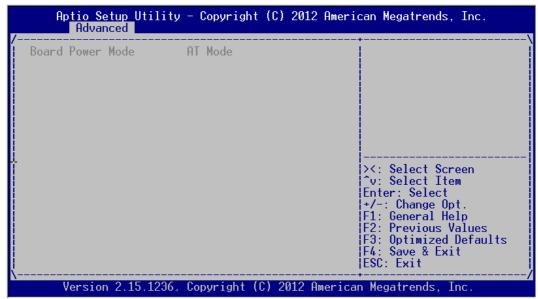

#### 4.2.2.8 APM Configuration

Figure 4.14: APM Configuration

#### Board Power Mode

This item is used to set power on mode: AT or ATX mode.

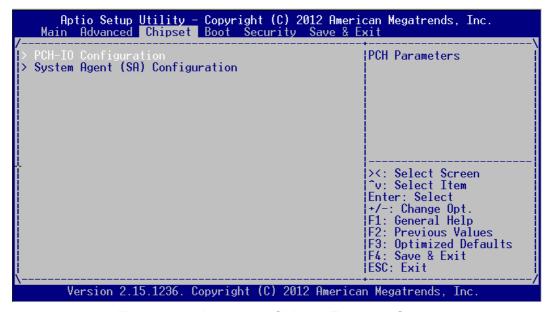

# 4.2.3 Advanced Chipset Features Setup

Figure 4.15 Advanced Chipset Features Setup

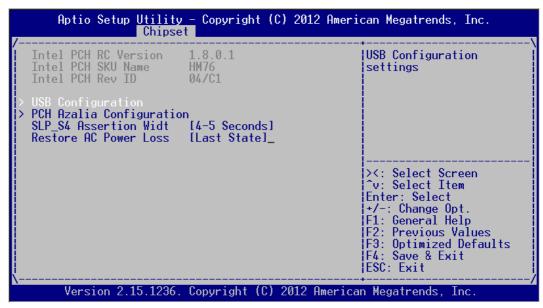

#### 4.2.3.1 PCH-IO Configuration

Figure 4.16 PCH-IO Configuration

#### ■ SLP S4 Assertion Width

This item is used to set the min. delay of SLP\_S4# signal when booting. The default setting is "4-5 Seconds".

#### Restore AC Power Loss

This item is used to set power status when the power in on.

Power Off: Power button should be pressed after the power is on.

Power On: No action required after the power is on.

Last State: Resume to the last state before the power is off.

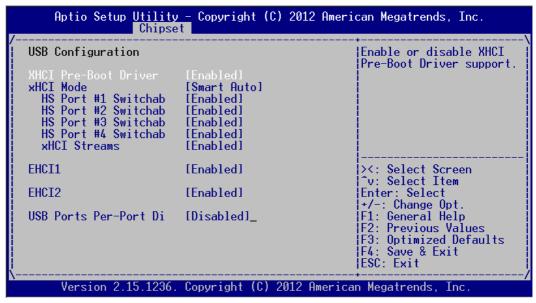

#### USB Configuration

Figure 4.17 Chipset USB Configuration

XHCI Pre-Boot Driver

This item allows users to enable or disable XHCI Pre-Boot Driver. The default setting is "Enable".

- xHCI Mode

This item is used to select xHCl controller mode. THe default setting is "Smart Auto".

HS Port #1/#2/#3/#4 Switchable

Enable: BIOS will let the port connect to EHCI; Disable: BIOS will let the port connect to xHCI. The default setting is "Enable".

xHCl Streams

This item allows users to enable or disable xHCl Maximum Primary Stream Array Size.

- EHCI1/EHCI2

This item allows users to enable or disable EHCI #1/EHCI #2. The default setting is "Enable".

USB Ports Per-Port Disable Control

This item is used to set disable control of each USB connector.

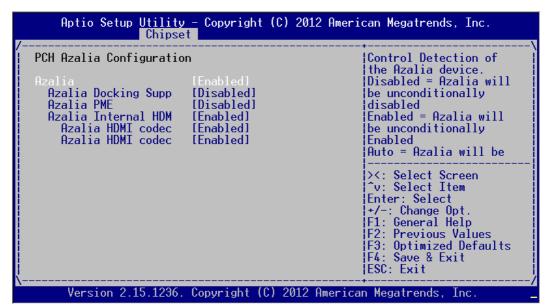

#### ■ PCH Azalia Configuration

Figure 4.18 PCH Azalia Configuration

Azalia

This item is used to detect Azalia device. The default setting is "Enable".

Disabled: Azalia will be unconditionally disabled.

Enabled: Azalia will be unconditionally Enabled.

Auto: Azalia will be enabled if present, disabled otherwise.

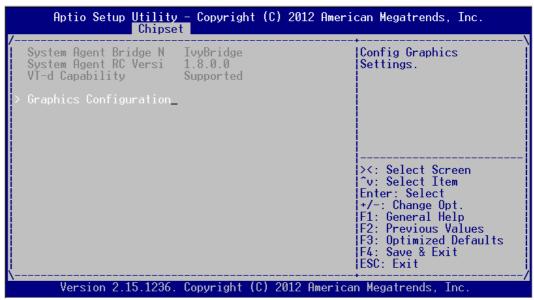

#### 4.2.3.2 System Agent (SA) Configuration

Figure 4.19: System Agent (SA) Configuration

#### Graphics Configuration

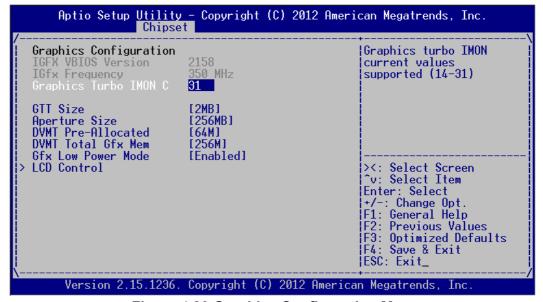

Figure 4.20 Graphics Configuration Menu

- Graphics Turbo IMON Current

Graphics turbo IMON current values supported (14-31).

- GTT Size

This item is used to select GTT size.

- DVMT Total Gfx Mem

- This item allows users to select memory size of DVMT Total.

- Gfx Low Power Mode

This item allows users to enable of disable Low Power mode.

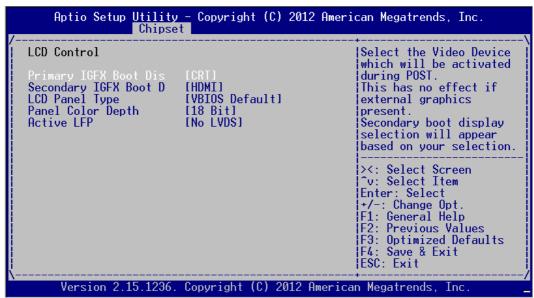

#### **LCD Control**

Figure 4.21 LCD Control

- Primary IGFX Boot Display This item is used to select video device started during POST. The default setting is "CRT".

- Secondary IGFX Boot Display This item is used to set Second Display Device.

- LCD Panel Type This item is used to set LCD resolution. The default setting is "1024x768(24bit)".

- Panel Color Depth This item is used to set LFP Panel Color Depth.

- This item is used to select Active LFP Configuration.

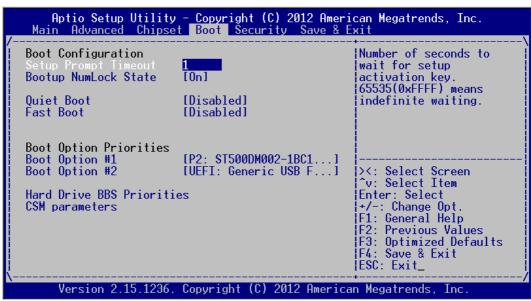

#### 4.2.4 Boot Setup

Figure 4.22: Boot Setup

#### 4.2.4.1 Boot Configuration

#### Setup Prompt Timeout

This item is the waiting time of pressing Setup button. If Setup button is not pressed within the setting time, system will continue to boot.

#### ■ Bootup NumLock State

This item allows users to active Bootup NumLock State function after the system is power on to DOS. The default setting is "On".

On: NumLock function is on when system boots.

Off: Cursor control is activated for keypad when system boots.

#### Quiet Boot

If it is set to "Disabled", BIOS will display normal POST information; If it is set to "Enabled", BIOS will show OEM icon rather than POST information.

#### ■ Fast Boot

This item allows BIOS to skip some testing procedures during booting so as to reduce system boot-up time. The default setting is "Disabled".

#### 4.2.4.2 Boot Option Priorities

```

Aptio Setup Utility - Copyright (C) 2012 American Megatrends, Inc.

Boot

Sets the system boot

[Generic USB Flash D...]

Boot Option #2

order

><: Select Screen

_v: Select Item</pre>

Enter: Select

+/-: Change Opt.

F1: General Help

F2: Previous Values

F3: Optimized Defaults

F4: Save & Exit

ESC: Exit

Version 2.15.1236. Copyright (C) 2012 American Megatrends, Inc

```

**Figure 4.23 Boot Option Priorities**

This item is used to set device boot sequence.

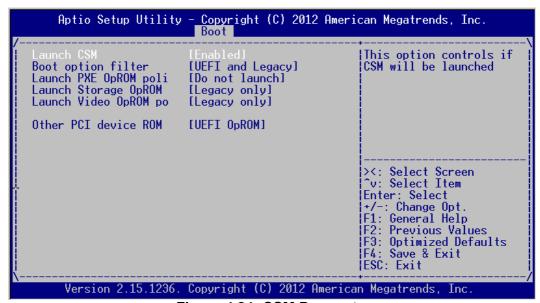

#### 4.2.4.3 CSM Parameter

Figure 4.24: CSM Parameter

#### **Launch CSM**

This item allows user to enable or disable CSM. The default setting is "Enable".

#### **Boot option filter**

This item is used to control boot device system. The default setting is "UEFI and Legacy".

#### Launch PXE OpROM policy

This item is used to control UEFI execution and backward compatibility of PXE OpROM. The default setting is "Do not Launch".

#### Launch Storage OpROM policy

This item is used to control UEFI execution and backward compatibility of PXE OpROM. The default setting is "Legacy only".

#### ■ Launch Video OpROM policy

This item is used to control UEFI execution and backward compatibility of PXE OpROM. The default setting is ""Legacy only".

#### Other PCI device ROM priority

This item is used for PCI device that is not the same as network, which is defined by massive storage or video booted by OpROM.

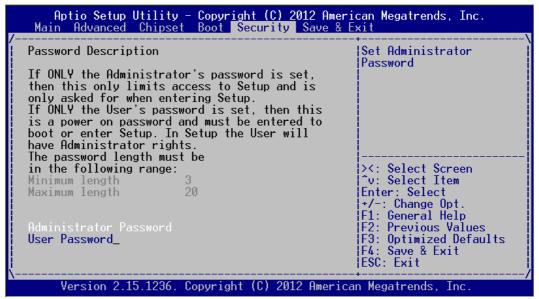

#### 4.2.5 Security Setup

Figure 4.25: Setup Security Menu

#### Administrator Password

This item is used to set Administrator Password.

#### User Password

This item is used to set User Password.

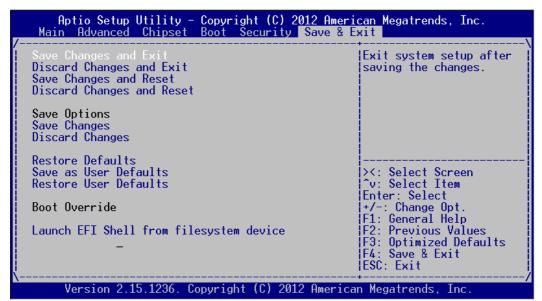

#### 4.2.6 Save & Exit Setup

Figure 4.26: Setup Save & Exit Menu

#### Save Changes and Exit

When you have completed system configuration, select this option to save your changes, exit BIOS setup and reboot the computer so the new system configuration parameters can take effect.

- 1. Select Save Changes and Exit from the Exit menu and press <Enter>. The following message appears:

- Save Configuration Changes and Exit Now? [Ok] [Cancel]

- 2. Select Ok or Cancel.

#### **Discard Changes and Exit**

Select this option to quit Setup without making any permanent changes to the system configuration.

- 1. Select Exit Discard Changes and Exit from the Exit menu and press < Enter>. The following message appears:

- Discard Changes and Exit Setup Now? [Ok] [Cancel]

- 2. Select Ok to discard changes and exit.

#### **Save Changes and Reset**

When you have completed system configuration, select this option to save your changes, exit BIOS setup and reboot the computer so the new system configuration parameters can take effect.

- 1. Select Save Changes and Reset and press < Enter>. The following message appears:

- Save configuration and Reset? [Yes] [No]

- 2. Select Ok or Cancel.

#### ■ Discard Changes and Reset

Select this option to quit Setup without making any permanent changes to the system configuration.

1. Select Discard Changes and Reset from the Exit menu and press <Enter>.

The following message appears: Discard Changes and Reset Setup Now?

[Ok] [Cancel]

2. Select Ok to discard changes and exit.

#### Save Changes

This item allows users to save changes done so far to any of the options.

#### Discard Changes

This item allows users to discard changes done so far to any of the options.

#### Restore Defaults

This item allows users to restore/load default values for all the options.

#### Save as User Defaults

This item allows users to save the changes done so far as user defaults.

#### Restore User Defaults

This item allows users to restore the user defaults to all the options.

#### Boot Override

This item allows users to set boot device.

#### ■ Launch EFI Shell from filesystem device

This item allows to boot EFI shell from system file device.

# Chapter

# **Driver Installation**

Sections include:

- **Chipset Windows Driver Setup**

- VGA Windows Driver Setup

- ME Windows Driver Setup

- LAN Windows Driver Setup

- USB 3.0 Windows Driver Setup

- Audio Windows Driver Setup

## 5.1 Introduction

Advantech offers a complete range of Device Driver and software supports for Windows programming developers. You can apply the Windows Device Drivers to the most popular Windows Programming tools, such as Visual C++, Visual Basic, Borland C++ Builder and Borland Delphi.

Here Windows 7 is taken as an example.

## 5.2 Driver Installation

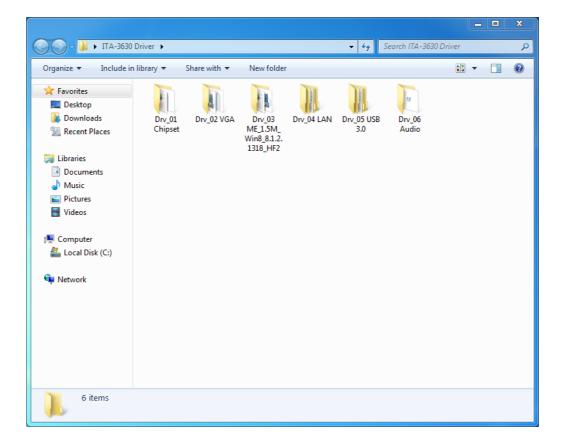

Insert the driver CD into your system's CD-ROM drive. You can see the ITA-5730 driver folder items.

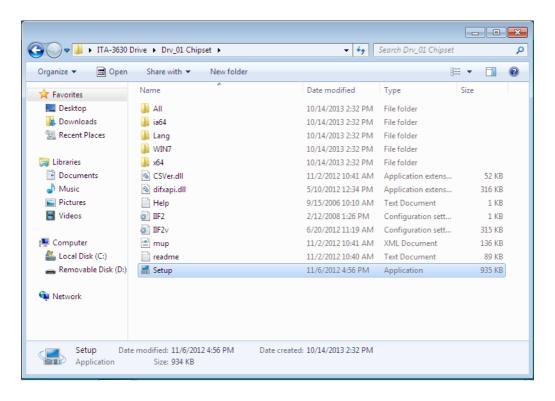

#### 5.2.1 Chipset Windows Driver Setup

Insert the driver CD into your system's CD-ROM drive. You can see the driver folder items. Navigate to the "Drv\_01Chipset" folder and click "Setup" to complete the installation of the driver.

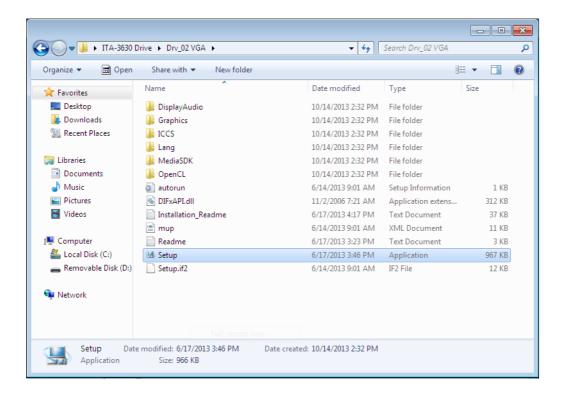

#### 5.2.2 VGA Windows Driver Setup

Insert the driver CD into your system's CD-ROM drive. You can see the driver folders items. Navigate to the "Drv\_02VGA" folder and click "Setup" to complete the installation of the drivers.

#### 5.2.3 ME Windows Driver Setup

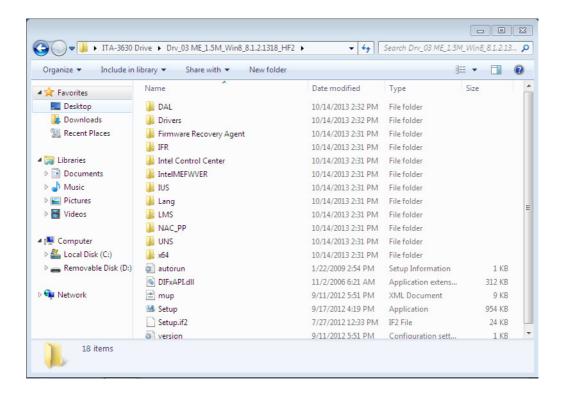

Insert the driver CD into your system's CD-ROM drive. You can see the driver folders items. Navigate to the "Drv\_03ME" folder and click "Setup" to complete the installation of the drivers.

# 5.2.4 LAN Windows Driver Setup

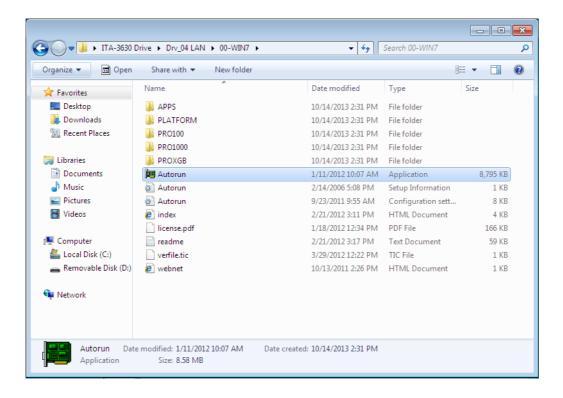

Insert the driver CD into your system's CD-ROM drive. You can see the driver folders items. Navigate to the "Drv\_04LAN" folder and click "Autorun" to complete the installation of the drivers.

#### 5.2.5 USB 3.0 Windows Driver Setup

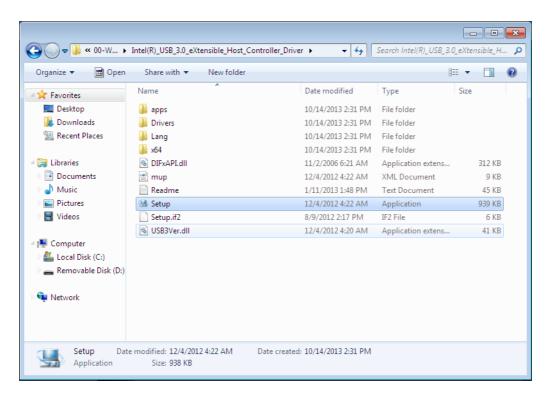

Insert the driver CD into your system's CD-ROM drive. You can see the driver folders items. Navigate to the "Drv\_05USB3.0" folder, and click "Setup" to complete the installation of the drivers.

#### 5.2.6 Audio Windows Driver Installation

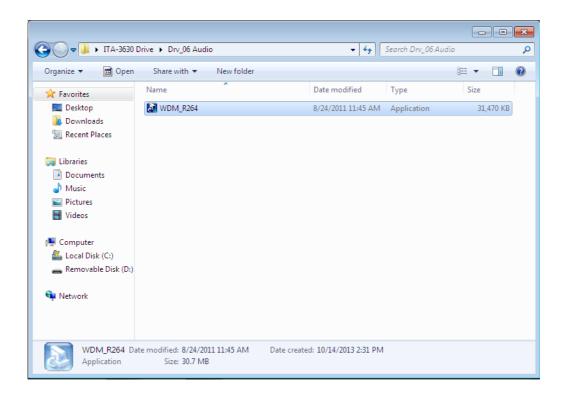

Insert the driver CD into your system's CD-ROM drive. You can see the driver folders items. Navigate to the "Drv\_ 06AUDIO" folder and click "WDM\_R264.exe" to complete the installation of the drivers.

# Chapter

6

# **GPIO Programming Guide**

This chapter introduces GPIO programming Guide.

Please carefully read and study the below screenshots and source codes in blue. Please download specification of NXP Semiconductors PCA955 for programming.

# **6.1 ITA-5730 Digital DIO Definition**

See Section 2.3.6.

# **6.2 Configuration Sequence**

ITA-5730's GPIO is realized through PCA9554 GPIO IC connected to ICH SMBUS. Therefore, the configuration and access to GPIO IC is completed by IO Space accessing to ICH SMBUS controller.

Below is the diagram of ICH SMBUS IO Space:

| SMB_BASE + Offset | Mnemonic  | REgister Name             | Default | Туре                        |

|-------------------|-----------|---------------------------|---------|-----------------------------|

| 00h               | HST_STS   | Host Status               | 00h     | R/WC, RO,<br>R/WC (special) |

| 02h               | HST_CNT   | Host Control              | 00h     | R/W, WO                     |

| 03h               | HST_CMD   | Host Command              | 00h     | R/W                         |

| 04h               | XMIT_SLVA | Transmit Slave<br>Address | 00h     | R/W                         |

| 05h               | HST_D0    | Host Data 0               | 00h     | R/W                         |

| 06h               | HST_D1    | Host Data 1               | 00h     | R/W                         |

For ITA-5730, IO address of the above SMB\_BASE is 0xF040.

The detailed SMBUS IO control access code, please refer to Chapter 3.

The corresponding SMBUS slave address of PCA9554 of GPIO 00 - GPIO 07 on ITA-5730 is 0x40 (8bit address):

GPIO 00 - GPIO 07: PCA9554 0x40 (IO0 - IO7)

#### Below is the sketch of PCA9554:

Table 2. Pin description

| Symbol          | Pin                             |              | Description |                               |

|-----------------|---------------------------------|--------------|-------------|-------------------------------|

|                 | DIP16, SO16,<br>SSOP16, TSSOP16 | HVQFN16      | SSOP20      | -                             |

| A0              | 1                               | 15           | 6           | address input 0               |

| A1              | 2                               | 16           | 7           | address input 1               |

| A2              | 3                               | 1            | 9           | address input 2               |

| 100             | 4                               | 2            | 10          | input/output 0                |

| IO1             | 5                               | 3            | 11          | input/output 1                |

| 102             | 6                               | 4            | 12          | input/output 2                |

| 103             | 7                               | 5            | 14          | input/output 3                |

| V <sub>SS</sub> | 8                               | 6 <u>[1]</u> | 15          | supply ground                 |

| 104             | 9                               | 7            | 16          | input/output 4                |

| 105             | 10                              | 8            | 17          | input/output 5                |

| 106             | 11                              | 9            | 19          | input/output 6                |

| 107             | 12                              | 10           | 20          | input/output 7                |

| ĪNT             | 13                              | 11           | 1           | interrupt output (open-drain) |

Below is the diagram of PCA9554 register:

#### 6.1.1 Command byte

Table 3. Command byte

| Command | Protocol        | Function                    |

|---------|-----------------|-----------------------------|

| 0       | read byte       | Input Port register         |

| 1       | read/write byte | Output Port register        |

| 2       | read/write byte | Polarity Inversion register |

| 3       | read/write byte | Configuration register      |

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers will be written or read.

PCA9554 has in all 4 registers to control GPIO.

#### PCA9554 register 0:

#### 6.1.2 Register 0 - Input Port register

This register is a read-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to this register have no effect.

The default 'X' is determined by the externally applied logic level, normally '1' when no external signal externally applied because of the internal pull-up resistors.

Table 4. Register 0 - Input Port register bit description

| Bit | Symbol | Access    | Value | Description                                  |

|-----|--------|-----------|-------|----------------------------------------------|

| 7   | 17     | read only | Χ     | determined by externally applied logic level |

| 6   | 16     | read only | Χ     |                                              |

| 5   | 15     | read only | Χ     |                                              |

| 4   | 14     | read only | Χ     |                                              |

| 3   | 13     | read only | Χ     |                                              |

| 2   | 12     | read only | Χ     |                                              |

| 1   | I1     | read only | X     |                                              |

| 0   | 10     | read only | Χ     |                                              |

If one GPIO Pin is set to Input, you can read input value from the bit that register 0 corresponds to.

#### PCA9554 register 1:

#### 6.1.3 Register 1 - Output Port register

This register reflects the outgoing logic levels of the pins defined as outputs by Register 3. Bit values in this register have no effect on pins defined as inputs. Reads from this register return the value that is in the flip-flop controlling the output selection, **not** the actual pin value.

Table 5. Register 1 - Output Port register bit description

Legend: \* default value.

| Bit | Symbol | Access | Value | Description                                       |

|-----|--------|--------|-------|---------------------------------------------------|

| 7   | 07     | R      | 1*    | reflects outgoing logic levels of pins defined as |

| 6   | O6     | R      | 1*    | outputs by Register 3                             |

| 5   | O5     | R      | 1*    |                                                   |

| 4   | 04     | R      | 1*    |                                                   |

| 3   | O3     | R      | 1*    |                                                   |

| 2   | 02     | R      | 1*    |                                                   |

| 1   | 01     | R      | 1*    |                                                   |

| 0   | 00     | R      | 1*    |                                                   |

If one GPIO Pin is set to Output, you can read input value from the bit that register 1 corresponds to.

#### PCA9554 register 2:

#### 6.1.4 Register 2 - Polarity Inversion register

This register allows the user to invert the polarity of the Input Port register data. If a bit in this register is set (written with '1'), the corresponding Input Port data is inverted. If a bit in this register is cleared (written with a '0'), the Input Port data polarity is retained.

Table 6. Register 2 - Polarity Inversion register bit description Legend: \* default value.

| Bit | Symbol | Access | Value | Description                                           |

|-----|--------|--------|-------|-------------------------------------------------------|

| 7   | N7     | R/W    | 0*    | inverts polarity of Input Port register data          |

| 6   | N6     | R/W    | 0*    | 0 = Input Port register data retained (default value) |

| 5   | N5     | R/W    | 0*    | 1 = Input Port register data inverted                 |

| 4   | N4     | R/W    | 0*    |                                                       |

| 3   | N3     | R/W    | 0*    |                                                       |

| 2   | N2     | R/W    | 0*    |                                                       |

| 1   | N1     | R/W    | 0*    |                                                       |

| 0   | N0     | R/W    | 0*    |                                                       |

If one GPIO Pin is set to Input, you can control the polarity of input pin from the bit that register 2 corresponds to.

#### PCA9554 register 3:

#### 6.1.5 Register 3 - Configuration register

This register configures the directions of the I/O pins. If a bit in this register is set, the corresponding port pin is enabled as an input with high-impedance output driver. If a bit in this register is cleared, the corresponding port pin is enabled as an output. At reset, the I/Os are configured as inputs with a weak pull-up to  $V_{DD}$ .

Table 7. Register 3 - Configuration register bit description Legend: \* default value.

| Bit | Symbol | Access | Value | Description                                     |

|-----|--------|--------|-------|-------------------------------------------------|

| 7   | C7     | R/W    | 1*    | configures the directions of the I/O pins       |

| 6   | C6     | R/W    | 1*    | 0 = corresponding port pin enabled as an output |

| 5   | C5     | R/W    | 1*    | 1 = corresponding port pin configured as input  |

| 4   | C4     | R/W    | 1*    | (default value)                                 |

| 3   | C3     | R/W    | 1*    |                                                 |

| 2   | C2     | R/W    | 1*    |                                                 |

| 1   | C1     | R/W    | 1*    |                                                 |

| 0   | C0     | R/W    | 1*    |                                                 |

Register 3 is used to set each GPIO as Input or Output:

If the bit is '0', the corresponding GPIO pin is set as Ouput;

If the bit is '1', the corresponding GPIO pin is set as Input.

#### Example:

Here take ITA-5730 as an example. Assume GPIO 00 is set as Output and GPIO 7 is set as Input, with two pins interconnected, how to set the corresponding register?

GPIO 00 corresponds to PCA9554 0x40 IO0, while GPIO 07 corresponds to PCA9554 0x40 IO7.

Set GPIO 00 as Output:

- 1. Read SMBUS slave 0x40 register 3 byte value;

- 2. Set bit 0 of the value read in step 1 as 0 and write it to SMBUS slave 0x40 register 3;

- 3. Read SMBUS slave 0x40 register 1 byte value;

- 4. Set bit 0 of the value read in step 3 as 0 or 1 according to low or high of the output value, then write it back to SMBUS slave 0x40 register 1.

#### Set GPIO 07 as Input:

- 1. Read SMBUS slave 0x40 register 3 byte value;

- 2. Set bit 7 of the value read in step 1 as 1 and write it to SMBUS slave 0x40 register 3;

- 3. Read SMBUS slave 0x40 register 0 byte value;

- 4. Decide low or high of the input value through bit7 value read in step3.

### 6.3 Function Call for Reference

#### **ICH SMBUS Access Code**

(The following code is realized by simulating the access of BIOS to SMBUS. It uses Borand C++ 3.1 for compiling and is successfully tested under DOS (So far, it is not tested under other OS).

```

#define SMBUS PORT 0xF040//SMB BASE?0xF040

typedef unsigned char BYTE;

BYTE

smbus read byte(BYTE addr, BYTE offset)

// Read SMBUS Register byte value. Read one byte value each time. addr is slave

address (such as 0x40), and offset is register offset.

{

int

i;

BYTE data;

outportb(SMBUS PORT + 4, (addr | 1));//

Write

slave

address

to

SMB_BASE + 4 (When reading, bit 0 of slave address should be set as 1, so here

addr|1 is available)

newiodelay();//delay

newiodelay();//delay

chk_smbus_ready();// Whether SMBUS is ready

```

3

outportb(SMBUS PORT + 3, offset);// Write register offset to SMB BASE +

```

newiodelay();//delay

newiodelay();//delay

outportb(SMBUS PORT + 2, 0x48);//

Write

SMBUS

command

to

SMB_BASE + 2. 0x48 means starting byte data transmission

newiodelay();//delay

newiodelay();//delay

for (i = 0; i \le 0x100; i++)

newiodelay();//longer delay

}

chk_smbus_ready();//Whether SMBUS is ready

return(inportb(SMBUS_PORT + 5));// Byte value read from SMB_BASE + 5

}

void

smbus write byte(BYTE addr, BYTE offset, BYTE value)

// Write SMBUS Register byte value. Write one byte value each time. addr is slave

address (such as 0x40), and offset is register offset.

{

int

i;

outportb(SMBUS PORT + 4, addr);// Write slave address to SMB BASE +

4 (When writing, slave address bit 0 should be set as 0)

moredelay();//longer delay

moredelay();//longer delay

chk_smbus_ready();//Whether SMBUS is ready

outportb(SMBUS_PORT + 3, offset);// Write register offset to SMB_BASE +

3

moredelay();//longer delay

moredelay();//longer delay

outportb(SMBUS_PORT + 5, value);//Write data value to SMB_BASE + 5

moredelay();//longer delay

moredelay();//longer delay

outportb(SMBUS_PORT + 2, 0x48);//

SMBUS

Write

command

to

SMB BASE + 2. 0x48 means starting byte data transmission.

moredelay();//longer delay

moredelay();//longer delay

for (i = 0; i \le 0x100; i++)

```

```

{

newiodelay();//longer delay

}

chk_smbus_ready();//?Whether SMBUS is ready

}

chk_smbus_ready()

//To decide whether SMBUS is ready or has completed the action, you should wait for

a long time to check whether SMBUS has successfully transmitted the command.

Since error may rarely occurs, BIOS code does not make judgement on the return