### Fully integrated controller for EPR USB-PD power supplies

# ST. ONEHP

### **Features**

- ZVS non-complementary active clamp flyback controller with synchronous rectification and USB-PD 3.1 EPR and AVS interface

- ARM® 32-bit Cortex®-M0+ MCU with 64 kB flash memory for digital power control and USB protocol

- FW programmable secondary side MCU controls both synchronous rectifier and ZVS active clamp flyback on the primary side to improve system efficiency in every condition

- High switching frequency operations in companion with MasterGaN power stage allow to use small size magnetic components, including planar transformers

- Reinforced galvanically isolated dual communication channel compliant with IEC 62368-1:

- 4 kV pk transient voltage

- 9.6 kV pk 1min hipot type testing

- 6.4 kV pk 1s hipot production testing

- 800 V high voltage startup with integrated input voltage sensing and Brownin/out functions

- Active input filter capacitor discharge circuitry for reduced standby power compliant with IEC 62368-1

- Fully Integrated USB-PD PHY with 24 V tolerant protection, and integrated load switch driver

# Product status link ST-ONEHP

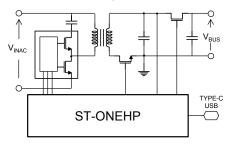

# Figure 1. Typical system block diagram

### **Application**

USB-PD 3.1 EPR chargers and adapters over 100 W for smartphones, tablets, laptops and other equipment

### **Description**

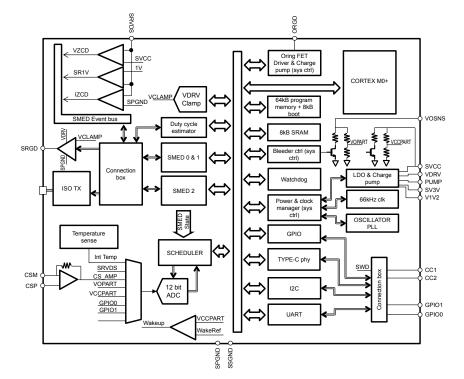

The ST-ONEHP is part of the ST-ONE® family, the world's first digital controllers embedding ARM Cortex M0+ core, an offline programmable controller with synchronous rectification, and USB PD PHY in a single package. Such a system is specifically designed to control ZVS non-complementary active clamp flyback converters to create high power density chargers and adapters with EPR compliant USB-PD interface.

The device includes an active clamp flyback controller and its HV startup on the primary side, a microcontroller and all the peripherals required to control the conversion and the USB-PD communication on the secondary side. The two sides are connected through an embedded galvanically isolated dual communication channel. By using a novel non-complementary control technique and specifically designed power modes the device allows to reach both high efficiency and low no load power consumption

The device is delivered with a pre-loaded firmware which handles both the power conversion and the communication protocols for EPR USB-PD including AVS and electronically marked cable management.

A dedicated memory stores a default device configuration during factory process. The user can change or adapt this memory area to fit the final product specifications.

# ST-ONEHP block diagram

Oring FET Driver & Ch. pump VDRV Clamp 3.3V LDO CORTEX M0+ SMEDs 8kB SRAM SS Timeout LEB SMED DEMODULATOR VDRV

PUMP

SV3V

V1V2 Temp sns SCHEDULER Int Temp SRVDS Power & clock manager (sys ctrl) SS\_MODE IS\_ON VOPART 12 bit ADC GPI00 TYPE-C phy **Q**2 I2C / UART SPGND CSM

Figure 2. ST-ONEHP block diagram

DS14224 - Rev 1 page 2/36

# 2 Pin connections and description

GPI00 HV GPI01 nc [ CSP nc [ hcsм nc 🗆 **∆**V1V2 POTP [ SSGND SSE SV3V OVP PVCC [ svcc Prosus PGND [ CC1 P3V3 [ DCC2 HON LON SSGND DORGD EN\_OUT [ SPGND osc DT SRGD SRVDS LEB DVDRV ISEN РИМР PGND

Figure 3. Pin connection (top view)

Table 1. Pin functions

| Pin   | Name   | Function                                                                                                                                                                                                                                                                                     |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |        | High voltage start-up generator / ac voltage sensing input. The pin, able to withstand 800 V, must be connected to the ac side of the input bridge via a pair of diodes to sense the ac input voltage.                                                                                       |

| 1     | HV     | When the voltage on the pin is higher than $V_{HVStart}$ , an internal pull-up circuit charges the capacitor connected between the pin PVCC and PGND.                                                                                                                                        |

|       |        | The pin is used also to sense the ac voltage, which is used by ac brown-out and X-cap discharge functions.                                                                                                                                                                                   |

| 2,3,4 | nc     | High voltage spacer. The pin is not connected internally to increase spacing between the high-voltage pin and the other pins.                                                                                                                                                                |

| 5     | POTP   | Primary side overtemperature protection. Pulling this pin below V <sub>POVTH</sub> shuts down the IC.                                                                                                                                                                                        |

| 6     | SS     | Soft-start setting. Connect a capacitor to PGND to set the soft-start duration.                                                                                                                                                                                                              |

| 7     | OVP    | Aux winding sense for overvoltage protection.                                                                                                                                                                                                                                                |

| 8     | PVCC   | Primary side supply voltage pin. The internal high voltage generator allows to charge an external capacitor connected between this pin and PGND before the converter starts up. A small bypass capacitor (0.1 µF typ.) to PGND must be placed close to the pins to get a clean bias voltage. |

| 9     | PGND   | Primary side ground. Reference for I/Os.                                                                                                                                                                                                                                                     |

| 10    | P3V3   | Primary side internal supply regulator bypass capacitor.                                                                                                                                                                                                                                     |

| 11    | HON    | High-side gate-drive control signal.                                                                                                                                                                                                                                                         |

| 12    | LON    | Low-side gate-drive control signal.                                                                                                                                                                                                                                                          |

| 13    | EN_OUT | Enable signal for an external driver. Improves efficiency during bursts in case the driver supports this functionality.                                                                                                                                                                      |

DS14224 - Rev 1 page 3/36

| Pin    | Name                                                                                 | Function                                                                                                                                                                                                     |

|--------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14     | osc                                                                                  | Oscillator pin. A resistor from the pin to PGND defines the switching frequency during the initial soft-start.                                                                                               |

| 15     | DT                                                                                   | Deadtime programming. A resistor from this pin to PGND sets the deadtime during soft-start and minimum deadtime during functional mode.                                                                      |

| 16     | LEB                                                                                  | Leading edge blanking time programming. A resistor from this pin to ground sets the leading edge blanking time for the ISEN comparator.                                                                      |

| 17     | ISEN                                                                                 | Current sense (PWM comparator) input. The voltage on this pin is compared with an internal reference to turn off LON.                                                                                        |

| 18     | PGND                                                                                 | Primary side signal ground. Reference for analog signals.                                                                                                                                                    |

| 19     | PUMP                                                                                 | Charge pump pin 1. Used to power the VDRV when SVCC drops below a programmable threshold.                                                                                                                    |

| 20     | VDRV                                                                                 | Driver supply.                                                                                                                                                                                               |

| 21     | SRVDS                                                                                | Output winding voltage sense. Connect to sync FET drain through a clamping MOSFET.                                                                                                                           |

| 22     | SRGD                                                                                 | Synchronous rectifier gate driver.                                                                                                                                                                           |

| 23     | SPGND                                                                                | Secondary side power ground. Current return for the sync FET gate-drive current.                                                                                                                             |

| 24     | ORGD                                                                                 | Load switch gate drive.                                                                                                                                                                                      |

| 24     | URGD                                                                                 | The pin is pulled to 5V above VOSNS to control an external circuit to drive a load switch.                                                                                                                   |

| 25     | SSGND                                                                                | Secondary side signal ground.                                                                                                                                                                                |

| 26 CC2 | USB Type-C CC2 pin. Used for USB-PD compliant communication or alternate function as |                                                                                                                                                                                                              |

| 20     | CC2                                                                                  | DN / GPIO3 / I2C-SCL / UART-TX. <sup>(1)</sup>                                                                                                                                                               |

| 27     | CC1                                                                                  | USB Type-C CC1 pin. Used for USB-PD compliant communication or alternate function as                                                                                                                         |

| 21     | CCT                                                                                  | DP / GPIO2 / I2C-SDA / UART-RX. <sup>(1)</sup>                                                                                                                                                               |

| 28     | VOSNS                                                                                | This pin provides a path for the output voltage bleeder. Connect to the USB connector VBUS through a clamping circuit.                                                                                       |

| 29     | SVCC                                                                                 | Secondary side VCC. The device senses and controls the converter output through this pin for output voltage lower than 15V.                                                                                  |

| 30     | SV3V                                                                                 | 3.3 V Regulated supply for the IC. Connect a 1µF capacitor from this pin to SSGND.                                                                                                                           |

| 31     | SSGND                                                                                | Secondary side signal ground.                                                                                                                                                                                |

| 32     | V1V2                                                                                 | 1.2 V regulated supply for the IC. Connect a 4.7µF capacitor from this pin to SSGND.                                                                                                                         |

| 33     | CSM                                                                                  | Output current sense pin. Connect to the negative side of sense resistor on the ground path.                                                                                                                 |

| 34     | CSP                                                                                  | Output current sense pin. Connect to the positive side of sense resistor on the ground path to sense the current drawn by the load.                                                                          |

| 35     | GPIO1                                                                                | General purpose digital I/O, used as output voltage sense through a resistor divider when the programmed output voltage is above a 15V (see SVCC pin).                                                       |

|        |                                                                                      | General purpose digital I/O, digital interface or analog input, not used with the pre-loaded firmware.                                                                                                       |

| 36     | GPIO0                                                                                | The pin is also used to enter in programming/boot mode at IC startup. Connect a $100k\Omega$ pullup to SV3V to avoid unwanted entry in boot mode at startup, unless this function is configured as disabled. |

The firmware loaded on ST-ONEHP configures the pins as either USB-PD or programming interface, depending on parameter setup. The default configuration is programming interface

DS14224 - Rev 1 page 4/36

# 3 Electrical ratings

Stresses above the absolute maximum ratings listed in Table 2. Absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute maximum ratings

| Symbol                                                    | Pin                     | Parameter                                | Value       | Unit |

|-----------------------------------------------------------|-------------------------|------------------------------------------|-------------|------|

| $V_{HV}$                                                  | HV                      | Voltage range (referenced to PGND)       | -1 to 800   | V    |

| V <sub>PVCC</sub>                                         | PVCC                    | Primary side supply voltage              | -0.3 to 18  | V    |

| V <sub>PV3V</sub>                                         | P3V3                    | 3.3 V supply range                       | -0.3 to 3.6 | V    |

| I <sub>OVP</sub>                                          | OVP                     | Maximum clamp source/sink current on OVP | -200 to 200 | μA   |

| V <sub>HON</sub> , V <sub>LON</sub> , V <sub>EN_OUT</sub> | HON, LON, EN_OUT        | Voltage range                            | -0.3 to 5.5 | V    |

| $V_{AMRPri}$                                              | Other primary side pins | Primary side analog Inputs & Outputs     | -0.3 to 3.6 | V    |

|                                                           | Secondary side          | voltages, referred to SSGND              |             |      |

| V <sub>CC1</sub> , V <sub>CC2</sub>                       | CC1, CC2                | USB connector IOs                        | -0.3 to 24  | V    |

| V <sub>VOSNS</sub> , V <sub>SVCC</sub>                    | VOSNS, SVCC             | Output voltage sense & VCC               | -0.3 to 24  | V    |

| $V_{PUMP}$                                                | PUMP                    | Charge pump pin, referred to SPGND       | -0.3 to 15  | V    |

| V <sub>ORGD</sub>                                         | ORGD                    | Oring FET gate driver voltage range      | -0.3 to 29  | V    |

| V <sub>CSP</sub> , V <sub>CSM</sub>                       | CSP,CSM                 | Current sense voltage range              | -0.3 to 3.6 | V    |

| V <sub>SV3V</sub>                                         | SV3V                    | 3 V supply voltage range                 | -0.3 to 3.6 | V    |

| V <sub>V1V2</sub>                                         | V1V2                    | 1.2 V supply voltage range               | -0.3 to 2   | V    |

| $V_{VDRV}$                                                | VDRV                    | Secondary side driver voltage            | -0.3 to 24  | V    |

| V <sub>SRGD</sub>                                         | SRGD                    | Sync FET gate driver voltage range       | -0.3 to 18  | V    |

| V <sub>SRVDS</sub>                                        | SRVDS                   | Drain sense voltage range                | -2 to 28    | V    |

| $V_{GPIO}$                                                | GPIO0,GPIO1             | GPIO voltage                             | -0.3 to 3.6 | V    |

| V <sub>SPGND</sub>                                        | SPGND                   | Power ground vs. signal ground           | -1 to 1     | V    |

Table 3. Maximum operating conditions

| Symbol                                                     | Pin               | Parameter                                       | Value        | Unit |

|------------------------------------------------------------|-------------------|-------------------------------------------------|--------------|------|

| V <sub>HV</sub>                                            | HV                | Voltage range (referenced to PGND)              | -1 to 450    | V    |

| V <sub>PVCC</sub>                                          | PVCC              | Primary side supply voltage                     | -0.3 to 16   | V    |

| C <sub>IO</sub>                                            | HON, LON, EN_OUT  | Capacitive load on primary side digital outputs | 0 to 10      | pF   |

| V <sub>CSP</sub> , V <sub>CSM</sub>                        | CSP,CSM           | Current sense voltage range                     | -0.3 to 1    | V    |

| V <sub>SVCC</sub> , V <sub>VOSNS</sub> , V <sub>VDRV</sub> | SVCC, VOSNS, VDRV | Secondary side voltage range                    | -0.3 to 22.5 | V    |

DS14224 - Rev 1 page 5/36

# 4 ESD immunity levels

Table 4. ESD immunity levels

| Mode | Pin | Reference specification | Value   | Unit |

|------|-----|-------------------------|---------|------|

| НВМ  | All | According to JS-001     | +/- 2   | kV   |

| CDM  | All | According to JS-002     | +/- 500 | V    |

DS14224 - Rev 1 page 6/36

# 5 Thermal data

Table 5. Thermal data

| Symbol                | Parameter                                              | Max. value | Unit |

|-----------------------|--------------------------------------------------------|------------|------|

| R <sub>th j-amb</sub> | Thermal Resistance, Junction-to-ambient <sup>(1)</sup> | 65         | °C/W |

| T <sub>J</sub>        | Junction Temperature Range                             | -40 to 125 | °C   |

| T <sub>STG</sub>      | Storage Temperature                                    | -55 to 150 | °C   |

<sup>1.</sup> Simulated, device mounted on 1s1p board

DS14224 - Rev 1 page 7/36

# 6 Safety data

Table 6. Insulation safety data according to IEC 62368

| Parameter                             | Value          |

|---------------------------------------|----------------|

| Insulation type                       | Reinforced     |

| Transient voltage                     | 4 kV           |

| Electric strength test (type test)    | 9.6 kV / 1 min |

| Electric strength test (routine test) | 6.4k V / 1 sec |

| Clearance                             | 8 mm           |

| Creepage                              | 8 mm           |

Table 7. Insulation safety data according to UL 1577

| Parameter                             | Value     |

|---------------------------------------|-----------|

| Isolation Voltage                     | 3770 Vrms |

| Transmitter maximum current           | 11 mA     |

| Receiver maximum current              | 91 mA     |

| Transmitter maximum power             | 1100 mW   |

| Receiver maximum current              | 130 mW    |

| Maximum operating ambient temperature | 85 °C     |

| Maximum junction temperature          | 125 °C    |

| Maximum storage temperature           | 150 °C    |

| Maximum data rate                     | 1 MHz     |

Table 8. X-Cap discharge safety data according to IEC 62368

| Parameter                | Value          |

|--------------------------|----------------|

| Maximum line voltage     | 240 Vrms + 10% |

| Overvoltage category     | II             |

| External capacitor value | 47 nF – 2.2 μF |

| Series resistor value    | 330 Ω – 4700 Ω |

DS14224 - Rev 1 page 8/36

# 7 Electrical data

$T_J$  = -40 to 125 °C,  $V_{PVCC}$  = 12 V,  $V_{SVCC}$  = 5 V , unless otherwise specified.

**Table 9. Electrical characteristics**

| Symbol                 | Parameter                          | Test Condition                              | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------|---------------------------------------------|------|------|------|------|

|                        |                                    | Primary side                                | '    |      |      |      |

| Supply volta           | ge                                 |                                             |      |      |      |      |

| V <sub>PVCCOn</sub>    | Turn-on threshold                  |                                             | 13   | 14   | 15   | V    |

| V <sub>PVCCOff</sub>   | UVLO / Restart threshold           |                                             | 6    | 6.5  | 7    | V    |

| V <sub>P3V3</sub>      | Primary side 3V3 regulator voltage | Iload < 4 mA                                | 3.1  | 3.3  | 3.5  | V    |

| Supply curre           | ent                                |                                             |      |      |      |      |

| I <sub>pq</sub>        | Quiescent current                  | Before turn-on                              |      |      | 0.55 | mA   |

|                        |                                    | Fsw=300 kHz,                                |      |      |      |      |

| I <sub>cc</sub>        | Operating supply current           | R <sub>DT</sub> =R <sub>LEB</sub> =12 kohm, |      | 2.8  |      | mA   |

|                        |                                    | $C_{EN}=C_{LON}=C_{HON}=10 pF$              |      |      |      |      |

| I <sub>burst</sub>     | Current during burst mode          |                                             |      |      | 1.1  | mA   |

| I <sub>qdis</sub>      | Shutdown quiescent current         | Device latched                              |      |      | 0.57 | mA   |

| High voltage           | start-up generator                 |                                             | '    |      |      |      |

| V <sub>HV</sub>        | HV breakdown voltage               | I <sub>HV</sub> < 100 μA                    | 800  |      |      | V    |

| V <sub>HVStart</sub>   | HV pin start-up voltage            |                                             |      | 30   |      | V    |

| V <sub>PVCC_SO</sub>   | Switchover threshold               |                                             |      | 1    |      | V    |

|                        |                                    | V <sub>HV</sub> > V <sub>HVStart</sub>      |      | _    |      |      |

|                        |                                    | V <sub>PVCC</sub> > V <sub>PVCC_SO</sub>    |      | 7    |      | mA   |

| I <sub>HVON</sub>      | ON-state current                   | V <sub>HV</sub> > V <sub>HVStart</sub>      |      |      |      |      |

|                        |                                    | V <sub>PVCC</sub> < V <sub>PVCC_SO</sub>    |      | 1    |      | mA   |

| I <sub>HVOFF</sub>     | Leakage current (Off-state)        | V <sub>HV</sub> = 400 V                     |      | 20   |      | μA   |

| X-cap discha           | arge                               |                                             |      |      |      |      |

| T <sub>XCDDET</sub>    | Detection time                     |                                             |      | 64   |      | ms   |

| V <sub>HVmin</sub>     | Peak residual voltage              | I <sub>HV,DIS</sub> > 4.2 mA                |      |      | 45   | V    |

| I <sub>HVDIS</sub>     | Discharge current                  | V <sub>HV</sub> > 45 V                      | 5    |      |      | mA   |

| V <sub>PVCCClamp</sub> | PVCC clamp voltage during X-cap    |                                             |      | 7    |      | V    |

| AC brown-in            | /out                               |                                             |      |      |      |      |

| V <sub>HVpk_BO</sub>   | Brown-out threshold                | Peak voltage                                | 94   | 100  | 106  | V    |

| V <sub>HVpk_BI</sub>   | Brown-in threshold                 | Peak voltage                                | 108  | 115  | 122  | V    |

| V <sub>HVpk_BI</sub>   | Brown-in/out hysteresis            | Peak voltage                                |      | 15   |      | V    |

| T <sub>BODG</sub>      | Brown-out deglitch time            |                                             | 48   | 60   | 72   | ms   |

| T <sub>DB_BI</sub>     | Brown-in deglitch time             |                                             |      | 500  |      | μs   |

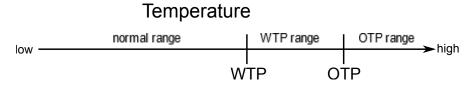

| Overtempera            | ature protection                   |                                             |      |      |      |      |

| V <sub>POVTH</sub>     | Overtemperature threshold          | Pin falling (temperature rising)            | 0.57 | 0.6  | 0.63 | V    |

DS14224 - Rev 1 page 9/36

| Symbol                | Parameter                                                     | Test Condition                          | Min. | Тур.  | Max. | Unit |

|-----------------------|---------------------------------------------------------------|-----------------------------------------|------|-------|------|------|

| V <sub>POVTH</sub>    | Overtemperature threshold                                     | Pin rising (temperature falling)        | 1.12 | 1.24  | 1.36 |      |

| I <sub>POTP</sub>     | POTP pull-up current                                          | V <sub>POTP</sub> = 0.6 V               | 18   | 20    | 22   | μА   |

| Soft-start            |                                                               |                                         |      |       |      |      |

| I <sub>SS</sub>       | Soft start current                                            | V <sub>SS</sub> = 0.25 V                | 1.7  | 2     | 2.3  | μА   |

|                       | Deadtine duration during                                      | R <sub>DT</sub> = 100 kΩ                | 240  | 300   | 360  | ns   |

| T <sub>DT_SS</sub>    | Deadtime duration during soft-start                           | R <sub>DT</sub> = 12.1 kΩ               | 32   | 40    | 48   | ns   |

|                       | 000                                                           | R <sub>OSC</sub> = 470 kΩ               | 8    | 10    | 12   | μs   |

| T <sub>OFFSS</sub>    | Off-time duration during soft-start                           | $R_{OSC}$ = 47 k $\Omega$               | 0.8  | 1     | 1.2  | μs   |

| V <sub>SSEND</sub>    | Soft-start timeout voltage                                    |                                         | 0.55 | 0.6   | 0.65 | V    |

| Overvoltage           |                                                               |                                         | 0.00 | 0.0   | 0.00 |      |

| - Torvortage          |                                                               |                                         |      |       |      |      |

| $V_{OVTH}$            | Overvoltage threshold (for flyback aux winding)               |                                         | 1.12 | 1.24  | 1.36 | V    |

| I <sub>OVTH</sub>     | Overvoltage threshold (for forward aux winding)               |                                         | 17   | 20    | 23   | μA   |

| V                     | Clamping voltage on OVP pin  OVP time filtering t protection  | OVP sourcing 20 uA                      | -0.1 | 0     | 0.1  | V    |

| V <sub>OVCLAMP</sub>  |                                                               | OVP sinking 20 uA                       | 3.1  | 3.3   | 3.5  | V    |

| T <sub>OVFILT</sub>   | OVP time filtering                                            |                                         | 2    | 4     | 6    | μs   |

| Overcurrent           | t protection                                                  |                                         | '    |       |      |      |

| V <sub>OCTH</sub>     | Overcurrent threshold                                         |                                         | 0.8  | 0.9   | 1.0  | V    |

| Burst mode            |                                                               |                                         |      |       |      |      |

| T <sub>TO</sub>       | IsoPWM absence time to trigger sleep mode entry               | From PWM falling edge                   |      | 60    |      | μs   |

| Current mod           | de unit                                                       |                                         |      |       |      |      |

| G <sub>TV</sub>       | Time to voltage conversion gain                               | IsoPWM Ton = 380 ns                     | 0.59 | 0.66  | 0.73 | V/µs |

| V <sub>IPKCLAMP</sub> | Maximum threshold                                             |                                         | 0.5  | 0.525 | 0.55 | V    |

|                       | Blanking time (from LON                                       | R <sub>LEB</sub> = 100 kOhm             | 240  | 300   | 360  | ns   |

| T <sub>LEB</sub>      | rising edge)                                                  | R <sub>LEB</sub> = 12.1 kΩ              | 33   | 41    | 49   | ns   |

| T <sub>CSDEL</sub>    | Total time between CS crossing and LON turn-off               | Including driver delay. dV/dt = 2 V/us. |      |       | 25   | ns   |

|                       | -                                                             | Time to 50%                             | 00   |       |      | >/   |

| V <sub>PCSOFF</sub>   | CS comparator offset                                          | D 40010                                 | -22  | 0     | 22   | mV   |

| $T_{DT}$              | LS to HS deadtime duration during normal                      | R <sub>DT</sub> = 100 kΩ                | 120  | 150   | 190  | ns   |

|                       | mode                                                          | R <sub>DT</sub> = 12.1 kΩ               | 15   | 22    | 30   | ns   |

| R <sub>LEB</sub> OPEN | protection (ROP)                                              |                                         |      |       |      |      |

| R <sub>LEB_OPEN</sub> | Maximum R <sub>LEB</sub> resistance to trigger the protection |                                         | 0.8  | 1.0   | 1.25 | ΜΩ   |

| IO electrical         | l data                                                        |                                         |      |       |      |      |

| $V_{OH}$              | LON/HON high voltage                                          | Pin sourcing 4 mA                       | 4    |       |      | V    |

| V <sub>OL</sub>       | LON/HON low voltage                                           | Pin sinking 4 mA                        |      |       | 0.4  | V    |

|                       |                                                               | Secondary side                          |      |       |      |      |

|                       |                                                               |                                         |      |       |      |      |

| Supply volta          | age                                                           |                                         |      |       |      |      |

| Supply volta          | Secondary side operative range                                |                                         | 3.05 |       | 22.5 | V    |

DS14224 - Rev 1 page 10/36

| Symbol              | Parameter                                                   | Test Condition                                                             | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| V <sub>SUVLO</sub>  | Secondary side UVLO threshold                               |                                                                            |      | 3    | 3.05 | V    |

| V <sub>SV3V</sub>   | Secondary side 3 V regulator voltage                        | Iload <sup>(1)</sup> < I <sub>SV3V</sub> (2 mA)<br>V <sub>SVCC</sub> > 3.3 | 3.1  | 3.2  | 3.3  | V    |

| I <sub>SV3V</sub>   | Maximum current capability from SV3V for external circuitry |                                                                            | 2    |      |      | mA   |

| V <sub>CPON</sub>   | Charge pump turn-on threshold (hysteretic mode)             | In burst mode                                                              |      | 8    |      | V    |

| V <sub>CPOFF</sub>  | Charge pump turn-off threshold (hysteretic mode)            | In burst mode                                                              |      | 8.4  |      | V    |

| Supply curr         | rent                                                        |                                                                            |      |      |      |      |

| I <sub>SVCC</sub>   | Operating supply current                                    |                                                                            |      | 18   |      | mA   |

| I <sub>sleep</sub>  | Deep sleep mode supply current                              | SVCC=5 V                                                                   |      | 1.4  |      | mA   |

| SR gate driv        | ver                                                         |                                                                            |      |      |      |      |

|                     |                                                             | SRDRVCONF <sup>(2)</sup> = 11                                              |      | 5    |      | V    |

| $V_{SRON}$          | SR driving voltage                                          | SRDRVCONF <sup>(2)</sup> = 10                                              |      | 7    |      | V    |

|                     |                                                             | SRDRVCONF <sup>(2)</sup> = 01                                              |      | 9    |      | V    |

|                     |                                                             | SRDRVCONF <sup>(2)</sup> = 00                                              |      | 11   |      | V    |

|                     |                                                             | Turn-on, time to 10%                                                       |      |      | 20   | ns   |

| T <sub>SRPROP</sub> | Driver propagation delay                                    | Turn-off, time to 90%                                                      |      | 15   | 20   | ns   |

| T <sub>SRRISE</sub> | Driver rise time                                            | 10% to 90%, 1 nF load                                                      |      | 40   | 65   | ns   |

| T <sub>SRFALL</sub> | Driver fall time                                            | 90% to 10%, 1 nF load                                                      |      | 20   | 40   | ns   |

| I <sub>DRVSRC</sub> | Driver source current                                       | ,                                                                          |      | 0.45 |      | A    |

| I <sub>DRVSNK</sub> | Driver sink current                                         |                                                                            |      | 0.6  |      | A    |

|                     |                                                             |                                                                            |      | 0.0  |      | ^    |

| Load Switch         | gate driver                                                 |                                                                            |      |      |      |      |

| I <sub>ORON</sub>   | Load switch turn-on current                                 |                                                                            |      | 10   |      | μA   |

|                     |                                                             | Referred to SVCC                                                           |      | _    | _    | T.,  |

| V                   | Load aviitala an valtana                                    | SVCC < 12 V                                                                | 4    | 5    | 7    | V    |

| V <sub>ORON</sub>   | Load switch-on voltage                                      | Referred to SVCC                                                           | 4    | _    | 6.5  | V    |

|                     |                                                             | SVCC >= 12 V                                                               | 4    | 5    | 0.5  | V    |

| Current sen         | se                                                          |                                                                            |      |      |      |      |

| V <sub>CSM</sub>    | CSM input range <sup>(3)</sup>                              |                                                                            | 0    |      | 50   | mV   |

| V <sub>SCSOFF</sub> | Current sense input offset                                  | Including ADC accuracy Input signal > 4 mV                                 | -0.5 |      | 0.5  | mV   |

| V <sub>CSFSR</sub>  | Current sense full scale range                              | CSP – CSM voltage                                                          |      | 25   |      | mV   |

| CMRR                | Common mode rejection                                       | 100 kHz – 1 MHz, 10 mV signal <sup>(4)</sup>                               | 50   |      |      | dB   |

| Voltage sen         |                                                             | , 5                                                                        |      |      |      |      |

| <u> </u>            |                                                             | VSET <sup>(5)</sup> = 00                                                   |      | 6    |      | V    |

| $V_{FSR}$           | Full scale range for SVCC                                   | VSET <sup>(5)</sup> = 01                                                   |      | 12   |      | V    |

| -                   | & VOSNS reading                                             | VSET <sup>(5)</sup> = 10                                                   |      | 24   |      | V    |

|                     | Cain array                                                  |                                                                            | 4    | 24   |      |      |

|                     | Gain error                                                  | Including ADC contribution $T_j = 0$ to 125 °C.                            | -1   |      | 1    | %    |

DS14224 - Rev 1 page 11/36

| Symbol               | Parameter                         | Test Condition                                                              | Min.                     | Тур.  | Max.                    | Unit |

|----------------------|-----------------------------------|-----------------------------------------------------------------------------|--------------------------|-------|-------------------------|------|

|                      | Offset                            | Including ADC contribution T <sub>j</sub> = 0 to 125 °C                     | -0.2% * V <sub>FSR</sub> |       | 0.2% * V <sub>FSR</sub> | V    |

| Adc                  |                                   |                                                                             |                          |       |                         |      |

| N <sub>bit</sub>     | Number of bits                    |                                                                             |                          | 12    |                         |      |

| INL                  | Integral non linearity            | 3% V <sub>REF</sub> < V <sub>IN</sub> < 95% V <sub>REF</sub> <sup>(4)</sup> | -3                       |       | 3                       | LSE  |

| DNL                  | Differential non linearity        | 3% V <sub>REF</sub> < V <sub>IN</sub> < 95% V <sub>REF</sub> <sup>(4)</sup> | -2                       |       | 2                       | LSE  |

| Wake-up co           | mparator                          |                                                                             |                          |       |                         |      |

|                      |                                   | DAC <sup>(2)</sup> = 0000, FSR <sup>(5)</sup> = 6 V                         |                          | 4.9   |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0001, FSR <sup>(5)</sup> = 6 V                         |                          | 4.95  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0010, FSR <sup>(5)</sup> = 6 V                         |                          | 5     |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0011, FSR <sup>(5)</sup> = 6 V                         |                          | 5.05  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0100, FSR <sup>(5)</sup> = 12 V                        |                          | 8.82  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0101, FSR <sup>(5)</sup> = 12 V                        |                          | 8.91  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0110, FSR <sup>(5)</sup> = 12 V                        |                          | 9     |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0111, FSR <sup>(5)</sup> = 12 V                        |                          | 9.09  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1100, FSR <sup>(5)</sup> = 24 V                        |                          | 11.76 |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1101, FSR <sup>(5)</sup> = 24 V                        |                          | 11.88 |                         | V    |

| $V_{WUP}$            | Wake-up threshold                 | DAC <sup>(2)</sup> = 1110, FSR <sup>(5)</sup> = 24 V                        |                          | 12    |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1111, FSR <sup>(5)</sup> = 24 V                        |                          | 12.12 |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1000, FSR <sup>(5)</sup> = 24 V                        |                          | 14.7  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1001, FSR <sup>(5)</sup> = 24 V                        |                          | 14.85 |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1010, FSR <sup>(5)</sup> = 24 V                        |                          | 15    |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 1010, FSR <sup>(5)</sup> = 24 V                        |                          | 15.15 |                         | V    |

|                      | -                                 | DAC <sup>(2)</sup> = 0000, FSR <sup>(5)</sup> = 24 V                        |                          | 19.6  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0001, FSR <sup>(5)</sup> = 24 V                        |                          | 19.8  |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0010, FSR <sup>(5)</sup> = 24 V                        |                          | 20    |                         | V    |

|                      |                                   | DAC <sup>(2)</sup> = 0011, FSR <sup>(5)</sup> = 24 V                        |                          | 20.2  |                         | V    |

|                      | Wake-up threshold                 | 27.0                                                                        | 0.00/                    |       | 0.00/                   | -    |

| V <sub>WUPACC</sub>  | accuracy                          |                                                                             | -0.9%                    |       | 0.9%                    |      |

|                      |                                   | HYST <sup>(2)</sup> = 00, FSR <sup>(5)</sup> = 6 V                          |                          | 13.5  |                         | m∨   |

| V <sub>WUPHYSY</sub> | Hysteresis                        | HYST <sup>(2)</sup> = 01, FSR <sup>(5)</sup> = 6 V                          |                          | 18    |                         | m∨   |

| WOFIIISI             | Tryotorodio                       | HYST <sup>(2)</sup> = 10, FSR <sup>(5)</sup> = 6 V                          |                          | 24    |                         | m۷   |

|                      |                                   | HYST <sup>(2)</sup> = 11, FSR <sup>(5)</sup> = 6 V                          |                          | 34.5  |                         | m۷   |

| SR compara           | ators                             |                                                                             |                          |       |                         |      |

| V <sub>THSR1V</sub>  | SR1V comparator threshold         |                                                                             | 0.7                      | 1     | 1.3                     | V    |

| T <sub>DSR1V</sub>   | SR1V comparator delay             | DVS falling @ 0.2 V/ns                                                      |                          | 20    | 30                      | ns   |

| V <sub>THIZCD</sub>  | IZCD threshold                    |                                                                             | -5                       | 0     | 2                       | mV   |

| T <sub>DIZCD</sub>   | IZCD comparator delay             | DVS rising @ 0.1 V/μs                                                       |                          | 50    | 80                      | ns   |

| V <sub>DYNZCD</sub>  | VZCD dynamic comparator threshold | Negative step starting from SVCC – 1 V                                      |                          | 1     |                         | V    |

| Bleeding re          | sistor                            |                                                                             |                          |       | <u> </u>                |      |

|                      | SVCC / VOSNS Bleeding             | ISET <sup>(6)</sup> = 0, V > 0.8 V                                          | 7                        | 10    |                         | mA   |

| I <sub>BLEED</sub>   | current                           | ISET <sup>(6)</sup> = 1, V > 0.8 V                                          | 14                       | 20    |                         | mA   |

DS14224 - Rev 1 page 12/36

| Symbol               | Parameter                                  | Test Condition                                                         | Min.  | Тур. | Max.  | Unit |

|----------------------|--------------------------------------------|------------------------------------------------------------------------|-------|------|-------|------|

| R <sub>CCBLD</sub>   | CC Bleeder resistance                      | V > 0.8 V                                                              |       | 2500 | 4000  | Ω    |

| Clock                |                                            |                                                                        |       |      |       |      |

|                      |                                            | T <sub>j</sub> = 0 – 125 °C                                            | 126.7 | 132  | 136.3 | MHz  |

| F <sub>CK</sub>      | Master clock frequency                     | T <sub>j</sub> = -40 – 125 °C                                          | 126.7 | 132  | 137.3 | MHz  |

| F <sub>CKLF</sub>    | Low frequency clock                        |                                                                        | 60    | 66   | 72    | kHz  |

| Internal tem         | perature sense                             |                                                                        |       |      |       |      |

| T <sub>ACC</sub>     | Temperature reading accuracy               | ADC reading <sup>(4)</sup>                                             | -10   |      | 10    | К    |

| GPIO electri         | ical data                                  |                                                                        |       |      |       |      |

| V <sub>OHGPIO</sub>  | GPIO0/1 high voltage                       | Pin sourcing 8 mA, digital mode                                        | 2.4   |      |       | V    |

| V <sub>OLGPIO</sub>  | GPIO0/1 low voltage                        | Pin sinking 8 mA, digital mode                                         |       |      | 0.4   | V    |

| V <sub>IHGPIO</sub>  | GPIO0/1 input high voltage                 | Digital mode                                                           | 2     |      |       | V    |

| V <sub>ILGPIO</sub>  | GPIO0/1 input low voltage                  | Digital mode                                                           |       |      | 0.8   | V    |

| VCONN                |                                            |                                                                        |       |      |       |      |

| R <sub>VCONN</sub>   | Vconn switch resistance to SVCC            | SVCC = 5 V                                                             |       | 20   |       | Ω    |

| CC cable co          | onnection wakeup                           |                                                                        |       |      |       |      |

| V <sub>THCCWUP</sub> | CC wake-up threshold                       |                                                                        | 2.5   | 2.6  | 2.7   | V    |

| CC Commu             | nication Wakeup                            |                                                                        |       |      |       |      |

|                      | CC communication threshold                 | Rising                                                                 |       | 0.85 |       | V    |

|                      | CC communication threshold                 | Falling                                                                |       | 0.25 |       | V    |

| CC OVP               |                                            |                                                                        |       |      |       |      |

| V <sub>CCOVP</sub>   | CC OVP threshold                           |                                                                        | 5.5   | 6    |       | V    |

| CC pullup            |                                            |                                                                        |       |      |       |      |

| ICCPUVMAX            | CC Pull-up current at V <sub>CCPUMAX</sub> | V <sub>CC</sub> = V <sub>CCPUMAX</sub> = 2.75 V                        | 30    |      |       | μА   |

|                      |                                            | ICCSET <sup>(7)</sup> = 01 V <sub>CC1</sub> = V <sub>CC2</sub> = 2.7 V | 64    | 80   | 96    | μA   |

| I <sub>CCPU</sub>    | CC Pull-up current                         | ICCSET <sup>(7)</sup> = 10 V <sub>CC1</sub> = V <sub>CC2</sub> = 2.7 V | 166   | 180  | 195   | μA   |

|                      |                                            | ICCSET <sup>(7)</sup> = 11 V <sub>CC1</sub> = V <sub>CC2</sub> = 2.7 V | 303   | 330  | 360   | μA   |

- 1. Iload is the current drawn by external circuits connected to SV3V pin.

- 2. This internal peripheral register is managed by the firmware according to the parameter configuration. See Device setup and User personalization

- 3. Current sense accuracy is not guaranteed if CSM pin voltage is beyond this range

- 4. Guaranteed by design.

- 5. This internal peripheral register is managed by the firmware depending on the output voltage setpoint. See Voltage sensing

- 6. This internal peripheral register is managed by the firmware. See Bleeding

- 7. This internal peripheral register is managed by the USB-PD protocol FW according to the standard

DS14224 - Rev 1 page 13/36

### 8 Device operation

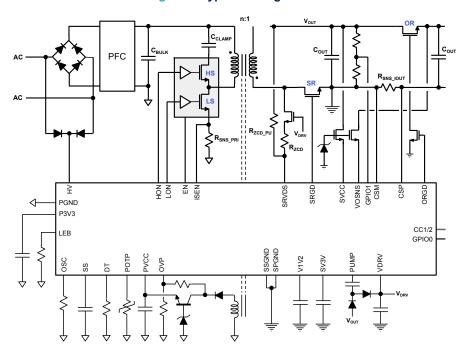

### 8.1 Typical application schematic

The following image is a simplified schematic for the typical application

Figure 4. Typical configuration

The ST-ONEHP is a very intergrated IC, which needs a few external components to build a complete system. On the primary side:

- An AC full wave power rectifier connected to a bulk capacitor, or a PFC if high power factor is required.

- Two rectifier diodes to provide HV voltage to ST-ONE IC both for high voltage startup and AC brownout and disconnection detection.

- An integrated half bridge power stage (e.g ST MasterGaN) or Gate driver + FETs connected to the transformer primary winding.

- A clamp capacitor to store the residual energy in the transformer leakage inductance.

- An auxiliary winding power supply for the IC PVCC, also used to perform overvoltage function during the soft-start.

### On the secondary side:

- A synchronous rectifier FET is connected to the SRGD pin.

- A cascode FET connected to the SRVDS pin to provide synchronous rectifier drain voltage sense while limiting the voltage on the pin below its AMR.

- A circuit connected to ORGD pin to drive a load switch to disconnect the output voltage as required by USB-PD power supplies.

- A sense resistor is connected to CSM/CSP pins to read the output current.

- A capacitor and two diodes connected to the PUMP pin to implement a charge pump providing the driving voltage to the synchronous rectifier.

- A clamp FET to limit the voltage on the SVCC to a value which must be below its maximum rating and above 15V

- A resistor divider to read the output voltage above 15V

- A clamp circuit to limit the voltage on VOSNS below its maximum rating

DS14224 - Rev 1 page 14/36

### 8.2 External component selection

### 8.2.1 Symbols used in this section

Ipk peak magnetizing current

$L_p$  primary side inductance

$L_k$  primary side leakage inductance

V<sub>i</sub> converter input voltage

Vo converter output voltage

n transformer turns ratio

$T_{sw}$  switching period

$f_{SW}$  switching frequency

$P_0$  converter output power

D duty cycle

$C_{ph}$  phase (switching) node total capacitance (typically, switch  $C_{oss}$  + transformer input capacitance)

C<sub>clamp</sub> clamp capacitor value

V<sub>priPk</sub> peak primary side voltage

f<sub>samp</sub> control loop sampling frequency

Cout output capacitor value

$V_{drop}$  voltage drop during step load transient

Istep load transient current step

### 8.2.2 Transformer design

### 8.2.2.1 Turns ratio

The ideal operating condition for a flyback is with duty cycle around 50%. The turns ratio is anyway limited by the voltage capability of the primary side switches.

As a first approximation, the turns ratio can be selected considering the maximum input and output voltage and selecting the highest value for which the voltage stress on the primary side switches is acceptable.

The voltage stress can be calculated as

$$V_{priPk} = V_i + nV_o + I_{pk} \sqrt{\frac{L_k}{C_{clamp}}} \tag{1}$$

The last term in the equation can be ignored for a first approximation, then considered after component selection. Typical turns ratio value for a 140W, 28V output USB-PD EPR application is around 4 to 4.5.

### 8.2.2.2 Primary side inductance – switching frequency

The ST-ONE Non complementary active clamp operates in a similar way as a quasi-resonant flyback, so as a first approximation the relation between the switching frequency and the primary side inductance can be calculated as

$$L_p = \left(\frac{V_i n V_o}{V_i - n V_o}\right)^2 \frac{1}{2f_{SW} P_o} \tag{2}$$

For a more accurate calculation the clamping time and the deadtimes must be considered, especially for high frequency converters. The following equation can be used to calculate the switching frequency when the system operates in ZVS:

$$T_{SW} = \frac{2L_p(V_i + V_{or}) \left( \frac{P_i(V_i + nV_o)}{V_i nV_o} + \sqrt{\frac{C_{ph} \left( V_i^2 - n^2 V_o^2 \right)}{L_p}} \right)}{V_i nV_o} + \frac{\pi \sqrt{L_p C_{ph}}}{2}$$

(3)

### 8.2.3 Clamp capacitor selection

The clamp capacitor value determines the resonance period between the capacitor and the transformer leakage inductance during phase 5 of the switching cycle (see Normal switching mode).

DS14224 - Rev 1 page 15/36

It is suggested to choose the clamp capacitor value so that the phase 5 lasts approximately 15% of the switching cycle in high line, high output voltage conditions, so

$$C_{clamp} \approx \frac{\left(0.15T_{SW}\right)^2}{\pi^2 L_{\nu}} \tag{4}$$

### 8.2.4 Secondary side drain sensing

The SRVDS pin is used for sensing the synchronous rectifier drain voltage to control turn-on and turn-off of the synchronous rectifier MOSFET and to sense the drain oscillations to operate in valley switching. The first function is performed by comparing SRVDS voltage with a 1 V and a 0 V internal threshold, while the second function is implemented by comparing the SRVDS voltage with SVCC.

A proper external clamp circuit is required to limit the voltage on the pin below its operative range while being able to correctly sense the MOSFET drain voltage from 0 V up to SVCC. A signal mosfet with gate tied to VDRV as shown the typical configuration schematic (see Figure 4) is the suggested solution. The resistors  $R_{ZCD}$  and  $R_{ZCDPU}$  in the schematic can be added to offset the signal and anticipate the IZCD comparator triggering.

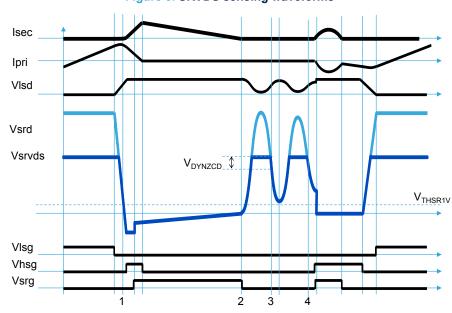

### 8.2.4.1 SRVDS comparators

The SRVDS pin has three comparators connected to it which are used to control the switching cycle.

The following figure shows the waveforms associated to the SRVDS comparators when the system is operating in valley skipping mode. The SR drain voltage is drawn as a light blue line, the clamped voltage on the SRVDS pin is shown in dark blue.

Figure 5. SRVDS sensing waveforms

**VZCD**: This comparator is used to count the switching node oscillations in valley skipping mode and to obtain valley turn-on. The comparator has a dynamic threshold, detecting when the voltage on SRVDS drops more than  $V_{DYNZCD}$  below the last peak reached. Referring to Figure 5, the comparator is triggered in instant 3 and 4

**IZCD**: This comparator compares SRVDS with SSGND. It is used to detect the zero crossing of the current during SR mos conduction phase. Referring to Figure 5, the comparator is triggered in instant 2.

**SR1V**: This comparator compares SRVDS with a 1 V threshold. It is used to detect when the primary side low side FET is turned off, making the voltage across the SR MOS drop. This comparator commands the turn-on of the SR mos. Referring to Figure 5, the comparator is triggered in instant 1.

### 8.2.5 Secondary side current sense resistor

The secondary side current sense has a full-scale range  $V_{CSFSR}$  equal to 25 mV. The current sense is chosen according to the formula:

DS14224 - Rev 1 page 16/36

$$R_{senseSec} < \frac{V_{CSFSR}}{I_{MAX}} \tag{5}$$

### 8.2.6 Voltage sense resistor divider

The secondary side voltage is read through an external resistor divider connected on the GPIO 1 pin whenever the voltage exceeds 15 V. The resistor divider ratio can be chosen by the user, the value shall be programmed in the device parameters to obtain the correct output voltage regulation.

The default value for the resistor divider is 14.96:1, which can be obtained using 127 k $\Omega$  and 9.1 k $\Omega$  resistors. This value is suggested for applications which provide up to 28 V on the output.

### 8.3 High voltage startup

The ST-ONE is equipped with internal HV start-up circuitry dedicated to supplying the IC during the initial start-up phase, before the self-supply winding is operating. An external capacitor connected to the PVCC pin is charged by the HV start-up circuitry, connected to the HV pin.

When the power is applied to the circuit and the voltage on the input is high enough, the HV generator is sufficiently biased to start operating, thus it draws the current  $I_{HVON}$  through the HV pin and charges the capacitor connected between PVCC pin and ground. This charging current is limited at 1 mA in case the voltage on PVCC is lower than  $V_{PVCC\ SO}$ , in order to prevent excessive IC dissipation if the pin is accidentally shorted to ground.

As the PVCC voltage reaches the start-up threshold (V<sub>PVCCOn</sub>) the chip starts operating, and the control logic disables the HV generator.

The IC is powered by the energy stored in the PVCC capacitor until the auxiliary winding develops a voltage high enough to sustain the operation.

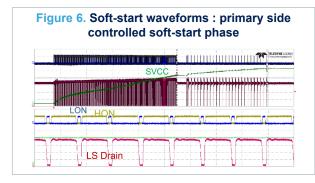

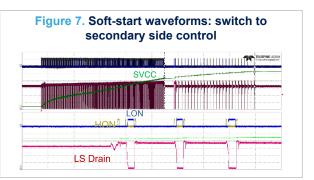

### 8.4 Soft-start

As soon as the proper conditions for startup are met, the primary side controller performs a soft-start autonomously until the secondary side is powered and able to take control of the switching.

During soft-start the IC operates in constant off-time, peak current mode. The user can set the off-time by connecting a resistor from the OSC pin to ground.

The peak current during soft-start is determined by comparing the SS pin and ISEN pin voltages. Connecting a capacitor to the SS sets the soft-start duration.

The primary side controlled soft-start ends as the secondary side takes control of the conversion.

During the soft-start the high-side is controlled in complementary mode, with deadtimes determined by a resistor connected between DT and ground. Note that during soft-start both the deadtimes are equal to  $T_{DT\_SS}$  which is approximately double the value used in normal mode for LS to HS.

As the voltage on the secondary side reaches  $V_{SVCCON}$  the secondary side IC boots up, takes control of the conversion and the converter starts to operate in normal mode as described in Section 8.5.1. The secondary side controller continues the soft-start operating in closed loop and ramping the SVCC voltage to 5 V, then the soft-start ends.

### 8.5 Switching modes

The following sections describe the switching modes which are used by the device depending on the output power to be delivered.

DS14224 - Rev 1 page 17/36

### 8.5.1 Normal switching mode

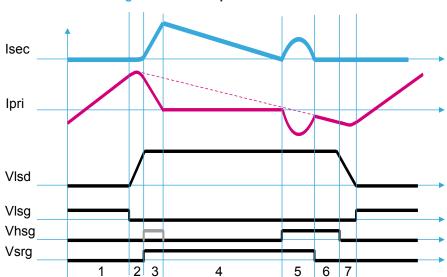

The controller operates a non-complementary active clamp converter. The main waveforms are shown in Figure 8.

Figure 8. Normal operation waveforms

The converter operation is similar to a traditional QR flyback, with the addition of a clamp switch to recover the energy in the transformer leakage inductance at low-side turn-off and uses the energy to obtain soft switching at low-side turn-on. In particular, the high-side is turned on for a time proportional to the input/output conversion ratio in order to limit the circulating current to what is required to obtain soft switching at low-side turn-on. The synchronous rectifier is kept on after high-side turn-on to obtain zero secondary side current before the high-side is turned off and a new cycle is started through a resonance between the leakage inductance and the clamp capacitor.

The phases are as follows:

- 1. LS turn-on. The on timing and peak current are defined by the secondary side controller. The phase terminates when the primary side peak current comparator is triggered.

- 2. Deadtime. A deadtime is inserted between LS turn-on and HS / SR turn-on.

- 3. SR turn-on / first HS turn-on. When the secondary side ZCD12 comparator is triggered, the secondary side commands the turn-on of both SR and HS switches. During this phase the current in the primary side leakage inductance drops to 0, while the energy is stored in the clamp capacitor. The HS switch turn-on is not strictly required but improves the efficiency of the system by avoiding conduction through the HS body diode. The duration of the first HS pulse can be controlled by the configuration parameters.

- 4. During phase 4 current flows on the secondary side through the SR FET. The phase terminates when the IZCD comparator is triggered (current on the secondary side reached 0).

- 5. HS is turned on to recover the energy stored in the clamp capacitor in phase 3 and to store energy in the primary side inductance to force a soft switching. During this phase the leakage inductance resonates with the clamp capacitor, creating a bump on the output current. When the current reaches 0 the SR is turned off. The duration of this phase is configured through programmable parameters.

- Extra HS turn-on time may be added to increase the energy stored in the magnetizing inductor, in particular

at low output and high input voltage. The firmware calculates the duration of this phase based on

parameters.

- Deadtime. The deadtime between HS and LS is controlled by the secondary side through the parameter DT HVG LVG.

### 8.5.1.1 Deadtime

Deadtime between LS on and HS on is set by connecting a resistor between DT pin and ground, according to the following formula:

DS14224 - Rev 1 page 18/36

$$t_{DT\_LS\_HS} = 3.88 \text{ns} + 1.46 \frac{\text{ns}}{\text{kO}} \cdot R_{DT}$$

(6)

Deadtime between HS and LS is instead controlled by the controller parameter DT\_HVG\_LVG according to the formula:

$$t_{DT\_HS\_LS} = \frac{DT\_HVG\_LVG}{F_{CK}} \tag{7}$$

Where  $F_{CK}$  is the IC clock frequency of 132 MHz.

### 8.5.1.2 Synchronous rectification voltage

The synchronous rectifier turn-on voltage is clamped to a programmable value. The user can choose the driving voltage which yields the best application performance.

The driver is powered from the VDRV pin.

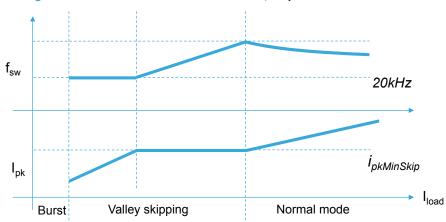

### 8.5.2 Skip mode

In order to improve the efficiency at medium load, the controller enters in valley skipping mode when the peak current falls below a programmable value.

While in skip mode the controller keeps the peak current approximately constant at the skipping mode entry point. If the frequency falls below approximately 20 kHz, the controller starts dropping the peak current while keeping the frequency limited between 20 kHz and a programmable value (typ. 50 kHz).

Figure 9. Transition between normal mode, skip mode and burst mode

### 8.5.3 Burst mode

While in skip mode, if the frequency drops below F<sub>CK</sub>/6500 (approximately 20 kHz) the system enters burst mode.

While in burst mode the controller generates bursts of pulses with a programmable peak current. The number of pulses generated depends on the output voltage and can be programmed through the parameters.

The system exits burst mode and comes back to normal operation when the average time between bursts drops below a programmable time.

### 8.5.3.1 Deep burst

When the regulated output voltage is 5 V or 9 V, all the IC functions are shut down between the bursts, leaving only a dedicated comparator to wake up the system when a new burst is required. In this condition, the consumption of the secondary side IC drops to  $I_{sleep}$ . For any other regulation voltage, the burst is controlled by the firmware and ADC readings, so the IC consumption between bursts is close to the normal mode operating current.

### 8.5.4 Special modes for voltage transitions

Protocols like USB-PD require to change the output voltage while the converter is operating following specific timing requirements. ST-ONEHP provides special operating modes to Manage negative transition while the applied load to the converter is very low.

DS14224 - Rev 1 page 19/36

### 8.5.4.1 Bleeding

The device integrates bleeding current sinks to discharge the output during negative voltage transitions which may happen at light load.

Bleeding current I<sub>BLEED</sub> is initially set to 10 mA, then increased to 20 mA.

### 8.5.4.2 Forced burst

In order to maintain the primary side PVCC powered, the IC forces bursts at regular intervals to recharge the primary side through its auxiliary winding.

### 8.5.4.3 Active bleeding mode

The IC can be configured to operate in a reverse flyback mode transferring energy from the output capacitor to the input bulk capacitor by switching the SR MOSFET.

This function is useful when the 20 mA bleeding current is not enough to meet the negative transition timing specifications, for example in applications with a big SVCC capacitor.

### 8.6 Control loop

The controller includes a peak current mode regulation loop to control the output voltage.

### 8.6.1 Voltage sensing

The IC senses the output voltage through a programmable resistor divider connected to the internal 12 bit ADC when the target voltage is below 15 V, otherwise the output voltage is sensed through an external resistor divider on pin GPIO0.

The internal resistor divider rescales the SVCC voltage so that the full scale can be configured as 6 V, 12 V or 24 V. The IC selects the scale depending on the target output voltage.

The thresholds for switching then internal scales are 5.8 V and 11.8 V, while the threshold to switch to the external divider is 15V.

During output voltage transitions, the greater scale between the initial and final voltages is used. At the end of the transition the scale is changed according to the final voltage.

For example in a transition from 5 V to 9 V the scale is initially switched to 12 V, at the end of the transition it is kept at 12 V scale. For a transition 9 V to 5 V, the scale is kept at 12 V and at the end of transition is changed to 6 V scale.

### 8.6.2 Peak current mode unit

The primary side low-side switch is controlled in peak current mode.

At every switching cycle LON stays high for the blanking time  $T_{LEB}$ . After the blanking time is expired, the LON is turned off when the CS comparator is triggered.

### 8.6.2.1 Reference generator

During normal operation the reference for the peak current mode control is provided by the secondary side through the galvanic isolation communication channel.

The primary side IC converts the duration of pulses received by the secondary side in a voltage reference for the peak current comparator according to the equation

$$v_{pk} = G_{TV}t_{pulse} \tag{8}$$

The reference voltage is limited by a hardware clamp to V<sub>IPKCLAMP</sub>.

The pulses are generated by the secondary side SMEDs.

### 8.6.3 Voltage loop

The voltage loop is managed by a digital PI (Type2) controller.

The device parameters control the proportional and integral gain of the controller. If sampling effects are ignored, the controller gain can be expressed as follows:

$$\frac{I_{peak}}{V_{err}} = \frac{G_{TV}}{R_{sense}} \frac{8}{F_{ck}V_{fsrMax}} \left( PID\_Pgain + \frac{1}{sT_{samp}} PID\_Igain \right) \tag{9}$$

DS14224 - Rev 1 page 20/36

Where  $R_{sense}$  is the primary side current sense resistor value, Fck is the clock frequency (132 MHz typ.),  $V_{fsrMax}$  is the ADC full scale range at the highest scale (24 V),  $G_{TV}$  is the time-voltage converter gain and  $T_{samp}$  is the control loop sampling period (30 us).

Considering the primary side peak current to average output current relation, the equation can be written as:

$$\frac{I_{Sec}}{V_{err}} = \frac{nV_{in}}{nV_{out} + V_{in}} \frac{G_{TV}}{R_{sense}} \frac{4}{F_{ck}V_{fsrMax}} \left( PID\_Pgain + \frac{1}{sT_{samp}} PID\_Igain \right) \tag{10}$$

Where n is the turns ratio (primary to secondary) and I<sub>sec</sub> is the transformer secondary side average current.

### 8.6.3.1 Setting the voltage loop parameters

The loop cutoff frequency is dominated by the proportional part of the controller, and can be approximated as: