## Automotive Audio Bus (A<sup>2</sup>B) Transceiver

## AD2431/AD2432/AD2433/AD2435

### **A<sup>2</sup>B BUS FEATURES**

### Line topology

- Single main node, up to 16 subordinate nodes Up to 15 m between nodes and up to 80 m overall cable

- length **Communication over distance**

- Synchronous data

- Multichannel I<sup>2</sup>S/TDM to I<sup>2</sup>S/TDM

- Clock synchronous, phase aligned in all nodes

- Low latency node to node communication

- Control and status information I<sup>2</sup>C to I<sup>2</sup>C

- **GPIO over distance**

- Bus power or local power subordinate nodes

- Configurable with SigmaStudio/SigmaStudio+ graphical software tool

- **AEC-Q100 qualified for automotive applications**

### **BASELINE A<sup>2</sup>B TRANSCEIVER FEATURES**

- Configurable as A<sup>2</sup>B bus main node or subordinate node Programmable via I<sup>2</sup>C and SPI interfaces

- 8-bit to 32-bit multichannel I<sup>2</sup>S/TDM interface

- I<sup>2</sup>S/TDM/PDM programmable data rate

- Up to 32 upstream and 32 downstream channels

- PDM inputs for 4 high dynamic range microphones on main or subordinate nodes

- Simultaneous I<sup>2</sup>S/TDM operations with up to 4 PDM microphones

### Unique ID register for each transceiver Support for crossover or straight-through cabling Programmable settings to optimize EMC performance

### **AD243x TRANSCEIVER ENHANCEMENTS**

### **Mixed Signal**

Up to 50 W A<sup>2</sup>B bus power Increased voltage regulator capacity (up to 100 mA) ADC monitoring of supply voltages Supports 3.3 V input at VIN in Low Voltage Input (LVI) mode Digital High speed SPI (up to 10 Mbps) over distance A<sup>2</sup>B bus self-discovery Dedicated hardware reset pin I<sup>2</sup>S/TDM crossbar switch Flexible mapping of Tx/Rx TDM channel data to A<sup>2</sup>B slot Support for I<sup>2</sup>C fast mode plus (1 MHz) Support for in cabin LED control using 4 PWM outputs 8 GPIO pins with configurable pin mapping **APPLICATIONS**

**Distributed audio systems** Personal audio zones In car communications Smart/remote tuner modules

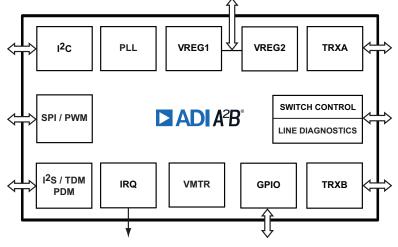

Figure 1. Functional Block Diagram

A<sup>2</sup>B and the A<sup>2</sup>B logo are registered trademarks of Analog Devices, Inc.

### Rev. SpB

### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### One Analog Way, Wilmington, MA 01887 U.S.A. ©2023 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# AD2431/AD2432/AD2433/AD2435

## **GENERAL DESCRIPTION**

The Automotive Audio Bus  $(A^2B^{\textcircled{b}})$  provides a multichannel, I<sup>2</sup>S/TDM link over distances of up to 15 m between nodes. It embeds bidirectional synchronous pulse-code modulation (PCM) data (for example, digital audio), clock, and synchronization signals onto a single unshielded twisted pair (UTP) differential cable. A<sup>2</sup>B supports a direct point to point connection and allows multiple, daisy-chained nodes at different locations to contribute and/or consume time division multiplexed channel content.

$A^2B$  is a single main node, multiple subordinate node system where the transceiver at the host controller is the main node. The main node generates clock, synchronization, and framing for all subordinate nodes. The main  $A^2B$  transceiver is programmable over a control port (I<sup>2</sup>C/SPI) for configuration and read back. An extension of the control port protocol is embedded in the  $A^2B$  data stream. This allows direct access to registers and status information on subordinate transceivers, as well as I<sup>2</sup>C to I<sup>2</sup>C, SPI to I<sup>2</sup>C, or SPI to SPI communication from the host to a peripheral in a subordinate node. SPI to SPI communication between subordinate nodes can be performed directly and does not need to involve the main node.

The transceiver can connect directly to general-purpose digital signal processors (DSPs), field-programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), microphones, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and codecs through a multichannel I<sup>2</sup>S/TDM interface. It also provides a pulse density modulation (PDM) interface for direct connection of up to four PDM digital microphones.

Finally, the transceiver also supports an  $A^2B$  bus powering feature, where the main node supplies voltage and current to the subordinate nodes over the same daisy-chained, twisted pair wire cable as used for the communication link.

Complete technical specifications are available for the A<sup>2</sup>B transceiver. Contact a2b.support@analog.com to complete the nondisclosure agreement (NDA) required to receive additional product information.

## Table 1. Product Comparison Guide

| Feature                          | AD2431      | AD2432        | AD2433             | AD2435        |

|----------------------------------|-------------|---------------|--------------------|---------------|

| Main node capable                | No          | No            | Yes                | Yes           |

| Functional TRX blocks            | A only      | A + B         | A + B              | A + B         |

| I <sup>2</sup> S/TDM support     | No          | No            | Yes                | Yes           |

| PDM microphone inputs            | 4 mics      | 4 mics        | 4 mics             | 4 mics        |

| A <sup>2</sup> B bus power       | N/A         | High (≤ 50 W) | Standard (≤ 2.7 W) | High (≤ 50 W) |

| Nominal bus bias voltage (VBUS)  | 7 V to 24 V | 7 V to 24 V   | 4 V to 9 V         | 7 V to 24 V   |

| SPI                              | No          | No            | Yes                | Yes           |

| Power configuration <sup>1</sup> | N/A         | CFG-4         | CFG-0              | CFG-4         |

<sup>1</sup>N/A means not applicable.

$I^2C$  refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2023 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D25790F-5/23(SpB)

www.analog.com