# TC35670FTG-006 Bluetooth® Smart + NFC Tag IC

**Rev 2.1**

Bluetooth SMART and Bluetooth are registered trademarks of Bluetooth SIG Inc.

ARM is a registered trademark of ARM Limited (or its subsidiaries) in the EU and/or elsewhere.

ARM7 is a trademark of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

FeliCa is a trademark of Sony Corporation.

FeliCa is a contactless IC card technology developed by Sony Corporation.

This product is produced under applicable FeliCa Lite-S technology license from Sony Corporation.

# **Contents**

| 1.             | General Description                                   | 5  |

|----------------|-------------------------------------------------------|----|

| 1.1.           | Product Concept                                       | 5  |

| 1.2.           | Features                                              | 5  |

| 2. F           | Pin Function                                          | 7  |

| 2.1.           | Pin Assignment (Top View) ver. P-VQFN40-0606-0.50-001 | 7  |

| 2.2.           | Pin Function Descriptions                             | 8  |

| 2.3.           | GPIO function list                                    | 14 |

| 2.4.           | Power Supply Pins                                     | 15 |

|                | System Configuration                                  |    |

| 3.1.           | Block Diagram                                         |    |

|                | Hardware Interfaces                                   |    |

| 4.1.           | Reset Interface (Power up sequence)                   |    |

| 4.1.           |                                                       |    |

| 4.1.           | •                                                     |    |

| 4.2.           | UART Interface                                        |    |

| 4.2.           |                                                       |    |

| 4.2.           |                                                       |    |

| 4.2.           |                                                       |    |

| 4.2.4          |                                                       |    |

| 4.2.           |                                                       |    |

|                | .2.5.1. HCI Reset                                     |    |

| 4.3.           | SPI Interface                                         |    |

| 4.3.           |                                                       |    |

| 4.3.2          |                                                       |    |

| 4.4.<br>4.4.   | I <sup>2</sup> C Interface                            |    |

|                |                                                       |    |

| 4.4.2          | ·                                                     |    |

| 4.5.           | PWM Interface                                         |    |

| 4.5.°<br>4.5.° |                                                       |    |

| 4.5. <i>i</i>  | ADC                                                   |    |

| 4.0.<br>4.6.   |                                                       |    |

| 4.6.           |                                                       |    |

| 4.7.           | IC Reference Clock Interface                          |    |

| 4.7.           |                                                       |    |

| 4.7.           |                                                       |    |

| 4.7.           | ·                                                     |    |

| 4.8.           | TAG- wireless interface                               |    |

| 4.8.           |                                                       |    |

| 4.8.           |                                                       |    |

| 4.8.           |                                                       |    |

| 4.8.4          |                                                       |    |

| 4.8.           |                                                       |    |

| 4.8.0          | ·                                                     |    |

| 4.9.           | TAG Wire Interface                                    |    |

| 4.9.           |                                                       |    |

| 4.9.           |                                                       |    |

| -              | 1                                                     |    |

| 4.9.3.         | Operation explanation                                               |    |

|----------------|---------------------------------------------------------------------|----|

| 4.9.4.         | Frame format                                                        |    |

| 4.9.5.         | Command type                                                        |    |

| 4.9.6.         | Operation Sequence                                                  |    |

| 4.9.7.         | Warning                                                             | 38 |

| 4.10.          | TAG Through function                                                | 39 |

| 4.10.1.        | Features                                                            | 39 |

| 4.10.2.        | Operation explanation                                               | 39 |

| 4.10.3.        | Packet Explanation                                                  | 40 |

| 4.10.4.        | Operation sequence                                                  | 43 |

| 5. TAG         | Built-in EEPROM and Block                                           | 46 |

| 5.1.           | Features                                                            | 46 |

| 5.2.           | Functional explanation                                              | 46 |

| 5.3.           | Block                                                               | 47 |

| 5.3.1.         | Block list                                                          | 47 |

| 5.3.2.         | Warning                                                             | 48 |

|                | t control TAG part                                                  |    |

| 6.1.           | Features                                                            |    |

| 6.2.           | Functional Explanation                                              |    |

| 6.3.           | Boot time                                                           |    |

| 6.4.           | Boot timing TAG part                                                |    |

|                | Clock control.                                                      |    |

| 7. TAG<br>7.1. | Features                                                            |    |

|                |                                                                     |    |

| 7.2.           | Functional Explanation                                              |    |

|                | Security functions                                                  |    |

| 8.1.           | Features                                                            |    |

| 8.2.           | Functional Explanation                                              |    |

|                | trical Characteristics                                              |    |

| 9.1.           | Absolute maximum rating                                             |    |

| 9.2.           | Operating Conditions                                                |    |

| 9.3.           | DC electric characteristics                                         |    |

| 9.3.1.         | Current Consumption                                                 |    |

| 9.4.           | Built-in Regulator Characteristics                                  | 56 |

| 9.5.           | ADC Characteristics                                                 | 56 |

| 9.6.           | RF Characteristics                                                  | 57 |

| 9.7.           | Rectifier circuit clamp charactersitic in TAG part                  | 59 |

| 9.8.           | Voltage detection characteristic in TAG part                        | 59 |

| 9.9.           | OSC frequency characteristic in TAG part                            | 59 |

| 9.10.          | Terminal capacitance in TAG part                                    | 59 |

| 9.11.          | EEPROM characteristic in TAG part                                   | 60 |

| 9.12.          | AC Interface Characteristics                                        | 61 |

| 9.12.1.        | UART Interface                                                      | 61 |

| 9.12.2.        | I <sup>2</sup> C Interface                                          | 62 |

| 9.12.          |                                                                     |    |

| 9.12.          |                                                                     |    |

| 9.12.3.        | SPI Interface                                                       |    |

| 9.12.4.        | I <sup>2</sup> C Interface TAG part                                 |    |

|                | em Configuration Example                                            |    |

| 10. Sysi       | In case of Host CPU connection                                      |    |

| 10.1.          | 111 (435 0) 1 1031 0 7 0 101 11 15 11 11 11 11 11 11 11 11 11 11 11 | 00 |

| 10.2.    | In case of Standalone       | 67 |

|----------|-----------------------------|----|

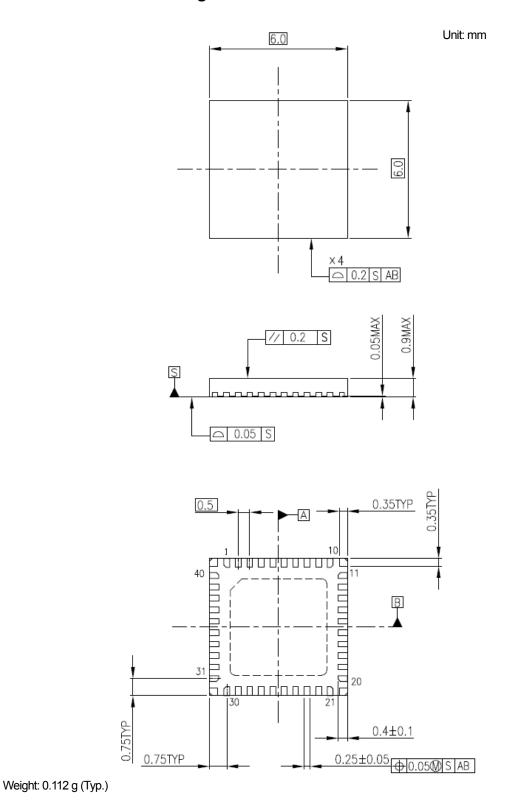

| 11. Pac  | kage outline                | 68 |

|          | Outline dimensional drawing |    |

| RESTRICT | IONS ON PRODUCT USE         | 69 |

## 1. General Description

#### 1.1. Product Concept

#### 1.2. Features

- Compliant with Bluetooth® Ver4.1 Low Energy

- ♦ Built-in Bluetooth<sup>®</sup> RF analog core and Baseband digital core

- ♦ Built-in ARM7TDMI-S<sup>®</sup> core (Internal CPU clock 13 MHz)

- ♦ On-chip Program Mask-ROM (320 KB)

- On-chip Work RAM for Bluetooth<sup>®</sup> communication process (96 KB),

On-chip RAM for application program storing (32 KB)

- ♦ Supports patch program loader function

- ♦ Supports sleep, deep sleep mode function.

- NFC Forum Type 3 Tag with wired interface

- ♦ Built-in FeliCa Contactless IC Card Technology

- Wireless interface: Automatic detection of transmission speed 212 kbps and 424 kbps

- ♦ I<sup>2</sup>C interface: Maximum operational clock 400 kHz

- Built-in EEPROM: General user area 1520 bytes, Highly reliable program function prevents from programming an incomplete data, Writing time:5 ms(typ.), 1 bit error automatic correction, CRC automatic addition, and error detection of read data.

- Security: Mutual authentication with Message authentication code (MAC).

Read only, read and write, read after authentication, write after authentication and data write with MAC are supported.

- General Purpose IO (9 pins)

- ♦ SPI interface (1 ch/General Purpose IO), I<sup>2</sup>C interface (1 ch/General Purpose IO), UART interface (1 ch/General Purpose IO)

- ♦ Host CPU Interface: UART interface (9600 bps to 921.6 kbps /General Purpose IO)

- ♦ Built-in general purpose ADC(2 ch for external inputs, 1 ch for internal VDD detection)

- ♦ Wake-up Interface (Wake-up input function from sleep and deep sleep /1 ch/General Purpose IO)

- → PWM Interface (1 ch/General Purpose IO)

- Base Clock Input

- Built-in oscillator for external resonator connection (26 MHz)

- ♦ Sleep Clock Input (External input supported 32.768 kHz)

- ➢ Built-in DCDC converter and LDO

- Wide range of input power supply voltage supported (Supply voltage 1.8 to 3.6 V, Low-voltage detection for batteries, DCDC start more than 2.0 V)

- Package:

- ♦ P-VQFN40-0606-0.50-001 [40 pin, 6 x 6 mm<sup>2</sup>, 0.5 mm pitch, 0.9 mm thickness]

\*FeliCa Technology refers to the following standards:

- JIS X 6319-4: Specification of implementation for integrated circuit (s) cards-Part 4: High speed proximity cards

- ISO/IEC 18092: Information technology -Telecommunications and information exchange between systems-Near Field Communication-Interface and Protocol-1(NFCIP-1)

- NFC Forum: <a href="http://www.nfc-forum.org/">http://www.nfc-forum.org/</a>

## 2. Pin Function

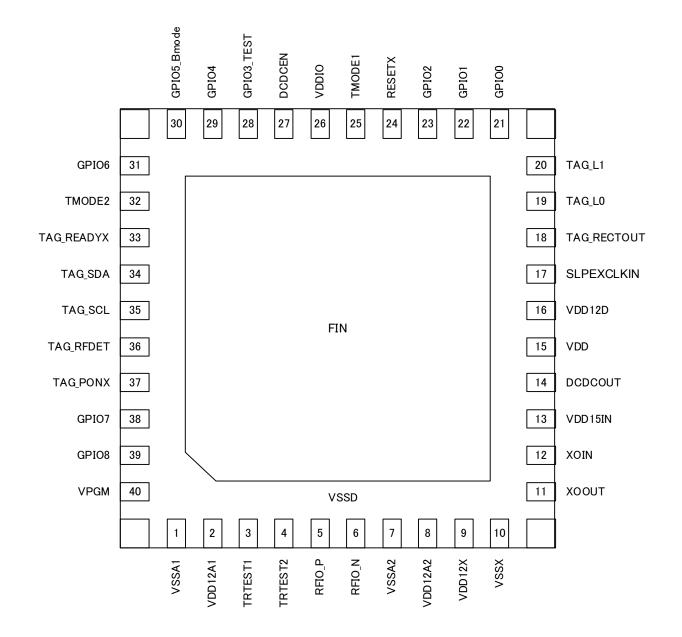

## 2.1. Pin Assignment (Top View) ver. P-VQFN40-0606-0.50-001

Figure 2-1 Pin Assignment (Top View)

# 2.2. Pin Function Descriptions

Table 2-1 shows attributes, input/output states for operating modes and descriptions for pin functions. Table 2-4 shows descriptions about power supply pins.

Table 2-1 Pin Functions

| Din name   | Dip No          | Attributo       | Condition       | Eupational description                               |  |  |  |

|------------|-----------------|-----------------|-----------------|------------------------------------------------------|--|--|--|

| Pin name   | Pin No          | Attribute       | Condition       | Functional description                               |  |  |  |

|            |                 | VDD category    | Default         |                                                      |  |  |  |

|            |                 | Direction       | (during reset)  |                                                      |  |  |  |

|            |                 | Туре            | D 1:1 f         |                                                      |  |  |  |

|            | Reset interface |                 |                 |                                                      |  |  |  |

| RESETX     | 24              | VDDIO           | -               | Hardware reset input pin.                            |  |  |  |

|            |                 | IN              |                 | Low:Reset                                            |  |  |  |

|            |                 | Schmitt trigger |                 |                                                      |  |  |  |

|            |                 |                 | DCDC enable pin |                                                      |  |  |  |

| DCDCEN     | 27              | VDDIO           | IN              | DCDC enable pin.                                     |  |  |  |

|            |                 | IN              |                 | High level: internal DCDC is ON                      |  |  |  |

|            |                 | Schmitt trigger |                 | Low level: internal DCDC is OFF                      |  |  |  |

|            | 1               |                 | Clock interface |                                                      |  |  |  |

| XOIN       | 12              | VDD12X          | IN              | Oscillator input pin for Baseband and RF reference   |  |  |  |

|            |                 | IN              |                 | clock (26 MHz) pin.                                  |  |  |  |

|            |                 | OSC             |                 | OSC's frequency accuracy should be ±50 ppm. A        |  |  |  |

|            |                 |                 |                 | feedback resistor is built in between XOIN pin and   |  |  |  |

|            |                 |                 |                 | XOUT pin.                                            |  |  |  |

|            |                 |                 |                 | This pin needs to be connected with the appropriate  |  |  |  |

|            |                 |                 |                 | resistor and capacitor for the connected X'tal.      |  |  |  |

| XOOUT      | 11              | VDD12X          | OUT             | Oscillator output for Baseband and RF reference      |  |  |  |

|            |                 | OUT             |                 | clock (26 MHz) pin A feedback resistor is built in   |  |  |  |

|            |                 | OSC             |                 | between XOIN pin and XOUT pin.                       |  |  |  |

|            |                 |                 |                 | This pin needs to be connected with the appropriate  |  |  |  |

|            |                 |                 |                 | resistor and capacitor for the connected X'tal.      |  |  |  |

| SLPEXCLKIN | 17              | VDDIO           | IN              | Sleep clock (32.768 kHz) input pin for low power     |  |  |  |

|            |                 | IN              |                 | consumption operation.                               |  |  |  |

|            |                 | OSC             |                 | Frequency accuracy of sleep clock should be ±500     |  |  |  |

|            |                 |                 |                 | ppm. When the clock is not supplied, this pin should |  |  |  |

|            |                 |                 |                 | be tied to GND.                                      |  |  |  |

|            |                 |                 | RF interface    |                                                      |  |  |  |

| RFIO_P     | 5               | VDD12A          | Hi-Z            | RF differential I/O pin.                             |  |  |  |

| RFIO_N     | 6               | IN/OUT          |                 | For external connection method of RF signal,         |  |  |  |

|            |                 | Analog          |                 | please refer to the attached connection              |  |  |  |

|            |                 | <u> </u>        |                 | configuration example.                               |  |  |  |

|            |                 |                 | TAG Interface   |                                                      |  |  |  |

| TAG_L0     | 19              | _               | Hi-Z            | TAG Antenna coil connection pin                      |  |  |  |

| TAG_L1     | 20              | IN/OUT          |                 |                                                      |  |  |  |

|            |                 | Analog          |                 |                                                      |  |  |  |

| Pin name   | Pin No | Attribute       | Condition      | Functional description                                   |

|------------|--------|-----------------|----------------|----------------------------------------------------------|

|            |        | VDD category    | Default        |                                                          |

|            |        | Direction       | (during reset) |                                                          |

|            |        | Туре            |                |                                                          |

| TAG_READYX | 33     | VDDIO           | OUT            | Through mode ready output pin                            |

|            |        | OUT             |                | When data of Through mode is received through            |

|            |        |                 |                | the wireless interface, this pin outputs low level.      |

|            |        |                 |                | If response data is received through the wired           |

|            |        |                 |                | interface, the level turns to the high level.            |

|            |        |                 |                | When not used, this pin should be opened.                |

| TAG_SDA    | 34     | VDDIO           | IN             | I <sup>2</sup> C interface for TAG                       |

|            |        | IN/OUT          |                | This pin can act as SDA in I <sup>2</sup> C.             |

|            |        | Schmitt trigger |                | When not used, this pin should be fixed to Low level     |

|            |        |                 |                | or High level.                                           |

| TAG_SCL    | 35     | VDDIO           | IN             | I <sup>2</sup> C interface for TAG                       |

|            |        | IN              |                | This pin can act as SCL in I <sup>2</sup> C.             |

|            |        | Schmitt trigger |                | When not used, this pin should be fixed to Low level     |

|            |        |                 |                | or High level.                                           |

| TAG_RFDET  | 36     | VDDIO           | Pull down      | TAG Carrier detection pin                                |

|            |        | OUT             | OUT            | If no TAG carrier, this pin becomes low level by         |

|            |        |                 |                | Pull-down.                                               |

|            |        |                 |                | If TAG wireless carrier is detected, this pin is cut off |

|            |        |                 |                | from Pull-down and becomes high level.                   |

| TAG_PONX   | 37     | VDDIO           | Pull up        | TAG Power supply switch controlling and wired            |

|            |        | IN              | IN             | interface enable pin.                                    |

|            |        | Schmitt trigger |                | In case of turning on power supply switch or using       |

|            |        |                 |                | the wired interface, input low level.                    |

|            |        |                 |                | High level leads to turning off the power supply         |

|            |        |                 |                | switch and disabling the wired interface                 |

|            |        |                 |                | When not used, this pin should be opened.                |

| Pin name | Pin No | Attribute       | Condition        | Functional description                                  |

|----------|--------|-----------------|------------------|---------------------------------------------------------|

|          |        | VDD category    | Default          |                                                         |

|          |        | Direction       | (during reset)   |                                                         |

|          |        | Туре            |                  |                                                         |

|          |        | Gene            | eral purpose I/O | port                                                    |

| GPIO0    | 21     | VDDIO           | Hi-Z             | General purpose I/O pin 0.                              |

|          |        | IN/OUT          |                  | During a reset and just after the reset release, this   |

|          |        | Pull up/        |                  | pin is set input-disabled.                              |

|          |        | Pull down       |                  | After the reset release, the firmware configures the    |

|          |        | Schmitt trigger |                  | pin function as wake up pin or general purpose IO pin.  |

|          |        |                 |                  | For sleep and deep sleep modes, after settings by       |

|          |        |                 |                  | firmware and external input, wake up function can       |

|          |        |                 |                  | be selected, which activates the chip.                  |

|          |        |                 |                  | When not used, this pin should be pulled down to        |

|          |        |                 |                  | the ground with 100 k $\Omega$ resistor.                |

| GPIO1    | 22     | VDDIO           | Analog           | ADC input and I/O Pin1.                                 |

|          |        | IN/OUT          |                  | During a reset, this pin is set input-disabled.         |

|          |        | Pull up/        |                  | After the reset is released, this pin is input-disabled |

|          |        | Pull down       |                  | with pull-up resistor off.                              |

|          |        | Schmitt trigger |                  | Then, this pin is controlled by firmware.               |

|          |        |                 |                  | After configuration by processing of firmware, that     |

|          |        |                 |                  | configures pull-up or pull-down resistors.              |

|          |        |                 |                  | Then the pin can function as general ADC-input 1 or     |

|          |        |                 |                  | general purpose IO pin.                                 |

|          |        |                 |                  | When not used, this pin should be pulled down to        |

|          |        |                 |                  | the ground.                                             |

| GPIO2    | 23     | VDDIO           | Analog           | ADC input and I/O Pin 2.                                |

|          |        | IN/OUT          |                  | During a reset, this pin is set input-disabled.         |

|          |        | Pull up/        |                  | After the reset is released, this pin is input-disabled |

|          |        | Pull down       |                  | with pull-up resistor off.                              |

|          |        | Schmitt trigger |                  | Then, this pin is controlled by firmware.               |

|          |        |                 |                  | After configuration by processing of firmware, that     |

|          |        |                 |                  | configures pull-up or pull-down resistors.              |

|          |        |                 |                  | Then the pin can function as general ADC-input 2,       |

|          |        |                 |                  | PWM output pin PWM0 or general purpose IO pin.          |

|          |        |                 |                  | When not used, this pin should be pulled down to        |

|          |        |                 |                  | the ground.                                             |

| Pin name   | Pin No | Attribute       | Condition      | Functional description                                 |

|------------|--------|-----------------|----------------|--------------------------------------------------------|

|            |        | VDD category    | Default        |                                                        |

|            |        | Direction       | (during reset) |                                                        |

|            |        | Туре            |                |                                                        |

| GPIO3_TEST | 28     | VDDIO           | Pull-up        | General purpose I/O pin 3.                             |

|            |        | IN/OUT          |                | During a reset, this pin is set input-disabled with    |

|            |        | Pull-up         |                | pull-up resistor on.                                   |

|            |        | Pull-down       |                | It becomes IC manufacture test mode in a Low           |

|            |        | Schmitt trigger |                | level input during the starting processing after reset |

|            |        |                 |                | release.Since Pull-up resistance checks the input      |

|            |        |                 |                | level of a pin in the state of On, please use it to be |

|            |        |                 |                | set to open or a High level.                           |

|            |        |                 |                | By the start processing of after releasing the reset,  |

|            |        |                 |                | UART1-TX, it will be set to the state of no Pull       |

|            |        |                 |                | resistance.Then, in the case of host program           |

|            |        |                 |                | download mode, assignment of UART1-TX is               |

|            |        |                 |                | canceled, and Pull-up resistance is set up.            |

|            |        |                 |                | This pin configures pull-up/pull-down resistance,      |

|            |        |                 |                | GPIO input or output, UART1-TX (UART2-TX), or          |

|            |        |                 |                | SPI-DOUT by a software process after normal            |

|            |        |                 |                | starting.                                              |

|            |        |                 |                | When not used, this pin should be opened.              |

| GPIO4      | 29     | VDDIO           | Pull-up        | General purpose I/O pin 4.                             |

|            |        | IN/OUT          |                | During a reset, this pin is set input-disabled with    |

|            |        | Pull-up         |                | pull-up resistor on. In the case of reset release in   |

|            |        | Pull-down       |                | using of stand-alone, it is set to a state in          |

|            |        | Schmitt trigger |                | UART1-RX without pull-up/pull-down resistance by       |

|            |        |                 |                | the start-up processing. In use by a stand-alone, an   |

|            |        |                 |                | external pull-up is always required. And, in the case  |

|            |        |                 |                | of host connection, please do not open or fixed to     |

|            |        |                 |                | the Low level at the time of start-up.                 |

|            |        |                 |                | Then, in the case of host program download mode,       |

|            |        |                 |                | assignment of UART1-RX will be canceled, and           |

|            |        |                 |                | Pull-up resistance will be set up.                     |

|            |        |                 |                | This pin configures pull-up/pull-down resistors, and   |

|            |        |                 |                | general purpose IO, UART1-RX (UART2-RX), or            |

|            |        |                 |                | SPI-DIN by a software process after normal             |

|            |        |                 |                | starting.When setting up as UART1-RX                   |

|            |        |                 |                | (UART2-RX), cautions are required so that the pin      |

|            |        |                 |                | may not be fixed to the Low level.                     |

|            |        |                 |                | (Please confirm firmware specifications for details.)  |

| Pin name    | Pin No | Attribute       | Condition      | Functional description                                  |

|-------------|--------|-----------------|----------------|---------------------------------------------------------|

|             |        | VDD category    | Default        |                                                         |

|             |        | Direction       | (during reset) |                                                         |

|             |        | Туре            |                |                                                         |

| GPIO5_Bmode | 30     | VDDIO           | Pull up        | General purpose I/O pin 5.                              |

|             |        | IN/OUT          |                | During a reset, this pin is input-disabled with pull-up |

|             |        | Pull up/        |                | resistor on. High input during power up sequence        |

|             |        | Pull down       |                | after reset enables host program download mode.         |

|             |        | Schmitt trigger |                | (In case of the pin in open will be the High-level      |

|             |        |                 |                | input by the internal pull-up.)                         |

|             |        |                 |                | After normal power up sequence with low input after     |

|             |        |                 |                | reset, the firmware configures pull-up/pull-down        |

|             |        |                 |                | resistors and general purpose IO, UART1-RTSX,           |

|             |        |                 |                | UART2-TX (UART1-TX), or SPI chip select output          |

|             |        |                 |                | pin SCS.                                                |

|             |        |                 |                | If this pin is always set to the Low level, the current |

|             |        |                 |                | will flow through the internal pull-up resistor.        |

|             |        |                 |                | Please remove the pull-up resistor by the setting       |

|             |        |                 |                | command after starting by the normal mode as            |

|             |        |                 |                | processing which reduces this current.                  |

|             |        |                 |                | (Please confirm firmware specifications for details.)   |

| GPIO6       | 31     | VDDIO           | Pull-up        | General purpose I/O pin 6.                              |

|             |        | IN/OUT          |                | During reset, this pin is input disabled with pull-up   |

|             |        | Pull-up         |                | resister on. After reset, firmware configures           |

|             |        | Pull-down       |                | pull-up/pull-down resistors and the pin can function    |

|             |        | Schmitt trigger |                | as GPIO, UART clear to send pin UART1-CTSX,             |

|             |        |                 |                | UART data receiver pin UART2-RX (UART1-RX),             |

|             |        |                 |                | or SPI data clock output pin SCLK. When not used,       |

|             |        |                 |                | this pin should be opened. When using as                |

|             |        |                 |                | UART2-RX (UART1-RX), cautions are required so           |

|             |        |                 |                | that the pin may not be fixed to the Low level.         |

| GPIO7       | 38     | VDDIO           | Pull-up        | General purpose I/O pin 7.                              |

|             |        | IN/OUT          |                | During reset, this pin is input disabled with pull-up   |

|             |        | Pull-up         |                | resister on. After reset, the firmware configures       |

|             |        | Pull-down       |                | pull-up/pull-down resistors and the pin can function    |

|             |        | Schmitt trigger |                | as GPIO, I2C-SCL pin, or SPI data output pin            |

|             |        |                 |                | DOUT When not used, this pin should be opened.          |

| GPIO8       | 39     | VDDIO           | Pull-up        | General purpose I/O pin 8.                              |

|             |        | IN/OUT          |                | During reset, this pin is input disabled with pull-up   |

|             |        | Pull-up         |                | resister on. After reset, the firmware configures       |

|             |        | Pull-down       |                | pull-up/pull-down resistors and the pin can function    |

|             |        | Schmitt trigger |                | as GPIO, I2C-SDA pin, orSPI data input pin DIN.         |

|             |        |                 |                | When not used, this pin should be opened.               |

| Pin name    | Pin No | Attribute       | Condition         | Functional description                            |

|-------------|--------|-----------------|-------------------|---------------------------------------------------|

|             |        | VDD category    | Default           |                                                   |

|             |        | Direction       | (during reset)    |                                                   |

|             |        | Туре            |                   |                                                   |

|             |        |                 | IC test interface |                                                   |

| TMODE1      | 25     | VDDIO           | _                 | Test mode setting pins                            |

| TMODE2      | 32     | IN              |                   | These pins are used for IC manufacturing test and |

|             |        | Schmitt trigger |                   | need to be connected to GND when assembled on     |

|             |        |                 |                   | a board.                                          |

|             |        |                 |                   |                                                   |

| TRTEST1     | 3      | VDD12A          | _                 | Analog test pins.                                 |

| TRTEST2     | 4      | IN/OUT          |                   | These pins are used for IC manufacturing test and |

|             |        | Analog          |                   | need to be connected to GND when assembled on     |

|             |        |                 |                   | a board.                                          |

|             |        |                 |                   |                                                   |

| TAG_RECTOUT | 18     | _               | Hi-Z              | Rectification circuit output pin                  |

|             |        | OUT             |                   | A signal receiving from TAG wireless interface,   |

|             |        | Analog          |                   | output from the rectification circuit can be      |

|             |        |                 |                   | monitored.                                        |

|             |        |                 |                   | When not used, this pin should be opened.         |

## 2.3. GPIO function list

GPIO pins can be assigned to UART I/Fs, serial memory I/Fs or some other functions by TC35670FTG firmware or command from external Hosts. Table 2-2 shows available functions for each GPIO pin, and Table 2-3 examples of GPIO function settings.

Table 2-2 Available functions for GPIO

| Pin         | Analog input Function 1 |             | Function 2 | Function 3 | Function 4 | Function 5 |

|-------------|-------------------------|-------------|------------|------------|------------|------------|

| GPIO0       | _                       | GPIO        | Wake Up    | _          | _          | _          |

|             |                         | Digital I/O | Input      |            |            |            |

| GPIO1       | ADC1 Input              | GPIO        | _          | _          | _          | _          |

|             |                         | Digital I/O |            |            |            |            |

| GPIO2       | ADC2 Input              | GPIO        | PWM0       | _          | _          | _          |

|             |                         | Digital I/O | Output     |            |            |            |

| GPIO3_TEST  | _                       | GPIO        | UART1-TX   | _          | SPI-DOUT   | UART2-TX   |

|             |                         | Digital I/O | Output     |            | Output     | Output     |

| GPIO4       | _                       | GPIO        | UART1-RX   | _          | SPI-DIN    | UART2-RX   |

|             |                         | Digital I/O | Input      |            | Input      | Input      |

| GPIO5_Bmode | _                       | GPIO        | UART1-RTSX | UART2-TX   | SPI-SCS    | UART1-TX   |

|             |                         | Digital I/O | Output     | Output     | Output     | Output     |

| GPIO6       | _                       | GPIO        | UART1-CTSX | UART2-RX   | SPI-SCLK   | UART1-RX   |

|             |                         | Digital I/O | Input      | Input      | Output     | Input      |

| GPIO7       | _                       | GPIO        | _          | I2C-SCL    | SPI-DOUT   | _          |

|             |                         | Digital I/O |            | Output     | Output     |            |

| GPIO8       | _                       | GPIO        | _          | I2C-SDA    | SPI-DIN    | _          |

|             |                         | Digital I/O |            | I/O        | Input      |            |

Note: Can be selected either GPIO8 or GPIO4 and GPIO7 or GPIO3\_TEST, SPI-DOUT, SPI-DIN is, can not be set for dual.

Table 2-3 GPIO function list (example)

| Pin name    | Basic      | Example of UART1           | Example of SPI     | Example of |

|-------------|------------|----------------------------|--------------------|------------|

|             | example    | + UART2 + I <sup>2</sup> C | + I <sup>2</sup> C | UART + SPI |

| GPIO0       | Wake Up    | Wake Up                    | Wake Up            | Wake Up    |

| GPIO1       | ADC-AIN1   | ADC-AIN1                   | ADC-AIN1           | ADC-AIN1   |

| GPIO2       | ADC-AIN2   | ADC-AIN2                   | ADC-AIN2           | PWM0       |

| GPIO3_TEST  | UART1-TX   | UART1-TX                   | SPI-DOUT           | UART1-TX   |

| GPIO4       | UART1-RX   | UART1-RX                   | SPI-DIN            | UART1-RX   |

| GPIO5_Bmode | UART1-RTSX | UART2-TX                   | SPI-SCS            | SPI-SCS    |

| GPIO6       | UART1-CTSX | UART2-RX                   | SPI-SCLK           | SPI-SCLK   |

| GPIO7       | I2C-SCL    | I2C-SCL                    | I2C-SCL            | SPI-DOUT   |

| GPIO8       | I2C-SDA    | I2C-SDA                    | I2C-SDA            | SPI-DIN    |

Note: There are other functions than the above examples. About the detail of the other functions, refer to TC35670FTG firmware specification.

# 2.4. Power Supply Pins

Table 2-4 shows the attributes and descriptions of power supply pins for normal operations.

Table 2-4 Power supply pins

| Pin name | Pin    | Attribute     | Description                                                                             |

|----------|--------|---------------|-----------------------------------------------------------------------------------------|

|          | number |               | ·                                                                                       |

|          |        | Туре          |                                                                                         |

|          |        | VDD/GND       |                                                                                         |

|          |        |               | VDD/GND                                                                                 |

| VPGM     | 40     | TEST          | Test pin                                                                                |

|          |        | _             | VPGM should be connected to GND directly.                                               |

| VDD      | 15     | DCDCIN        | Power supply pin for DCDC and sleep circuit.                                            |

|          |        | VDD           | When internal DCDC is not used, this pin needs to be connected to the power             |

|          |        |               | supply.                                                                                 |

| VDDIO    | 26     | Digital       | Power supply pin for GPIO and TAG.                                                      |

|          |        | VDD           | This pin inputs the voltage for supply to the GPIO pin.                                 |

| DCDCOUT  | 14     | DCDCOUT       | DCDC output pin.                                                                        |

|          |        | _             | Connect to VDD15IN pin.                                                                 |

| VDD15IN  | 13     | LDOIN         | Power supply pin for internal regulator.                                                |

|          |        | VDD           | When DCDCEN pin is connected to VDD, this pin needs to be connected to                  |

|          |        |               | DCDCOUT.                                                                                |

|          |        |               | When DCDCEN pin is connected to GND, this pin needs to be connected to                  |

|          |        |               | external power supply.                                                                  |

| VDD12A1  | 2      | Analog        | LDO output 1.2 V is supplied to internal analog circuit.                                |

|          |        | VDD           | A capacitor of 0.1 $\mu\text{F}$ or more at the operating temperature range needs to be |

|          |        |               | connected as the load of the LDO.                                                       |

| VDD12D   | 16     | Digital       | LDO output 1.1 V is supplied to internal digital circuit.                               |

|          |        | VDD           | A capacitor of 0.1 $\mu\text{F}$ or more at the operating temperature range needs to be |

|          |        |               | connected as the load of the LDO.                                                       |

| VDD12X   | 9      | Analog        | LDO output 1.2 V is supplied to internal OSC circuit.                                   |

|          |        | VDD           | A capacitor of 0.1 $\mu\text{F}$ or more at the operating temperature range needs to be |

|          |        |               | connected as the load of the LDO.                                                       |

| VDD12A2  | 8      | Analog        | LDO output 1.2 V is supplied to internal analog circuit.                                |

|          |        | VDD           | A capacitor of 0.1 $\mu\text{F}$ or more at the operating temperature range needs to be |

|          |        |               | connected as the load of the LDO.                                                       |

| VSSA1    | 1      | Analog        | GND pin for analog, this pin needs to be connected to GND.                              |

|          |        | GND           |                                                                                         |

| VSSA2    | 7      | Analog<br>GND | GND pin for analog, this pin needs to be connected to GND.                              |

| VSSX     | 10     | Analog<br>GND | GND pin for OSC, this pin needs to be connected to GND.                                 |

| VSSD     | FIN    | Digital       | Die pad and Fin. Connect the exposed Die Pad and Fin portion to digital GND.            |

|          | ' ' '  | GND           |                                                                                         |

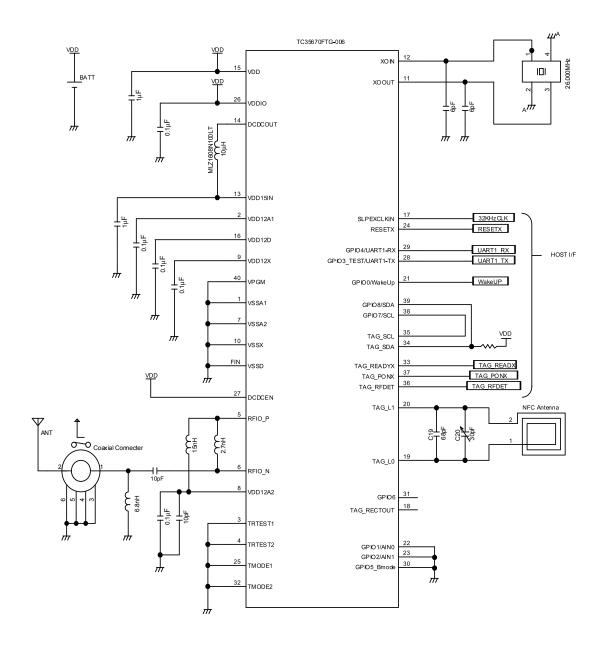

## 3. System Configuration

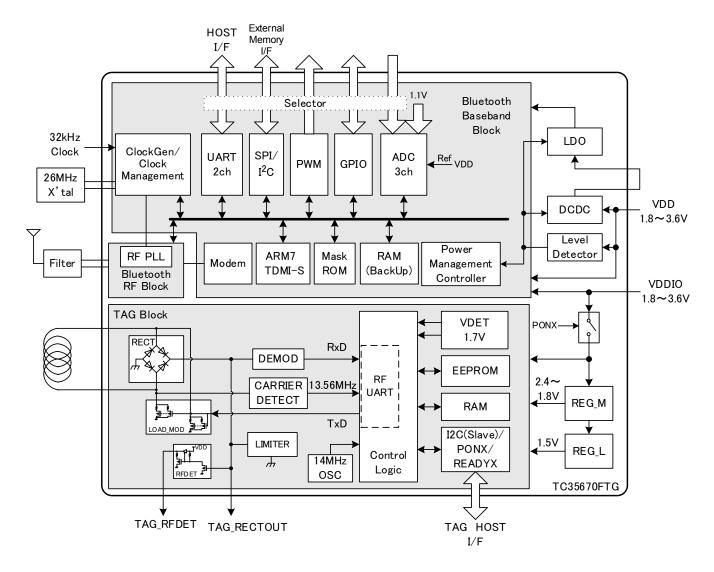

## 3.1. Block Diagram

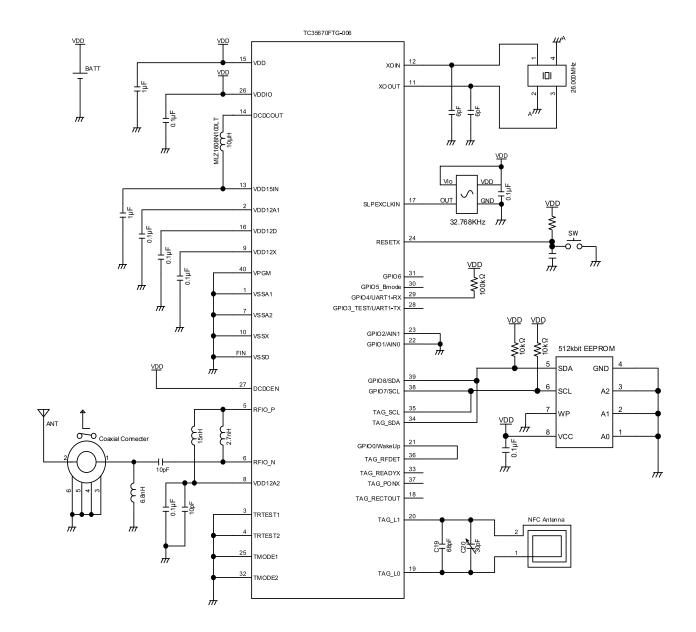

Figure 3-1 shows block diagram of TC35670FTG.

TC35670FTG is powered by single voltage between 1.8 V and 3.6 V.

The chip has built-in DCDC and LDO requiring external capacitors.

It uses 26 MHz base clock and 32.768 kHz sleep clock.

External Memory Interface is SPI or I<sup>2</sup>C, and host CPU interface is UART.

TAG uses the I<sup>2</sup>C interface that is separate from the serial memory connection.

Figure 3-1 Example of TC35670FTG system configuration

#### 4. Hardware Interfaces

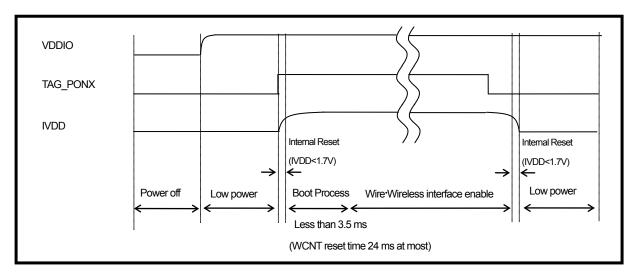

## 4.1. Reset Interface (Power up sequence)

#### 4.1.1. Features

Reset interface has the following features.

- > 1.8 to 3.6 V operation

- Level sensitive asynchronous reset (Low level: reset)

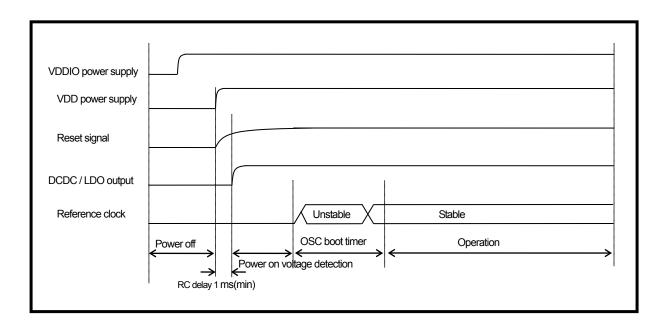

The reset signal should be at reset status (RESETX = Low) when the power is turned on. Once the power supply has become stable, disabling the reset signal (RESETX = High) starts the X'tal oscillation after DCDC output has become stable If DCDC is used, or after each LDO output has reached its target voltage. Then, an internal timer releases internal reset 1 ms after the X'tal oscillation has become stable.

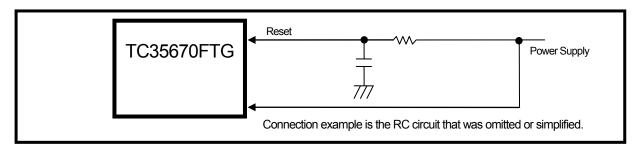

#### 4.1.2. Connection Example

Figure 4-1 shows connection example where TC35670FTG is RC time constant circuit.

Reset signal can be given by RC time constant circuit on the power-supplied, or can be connected with an IC which has asynchronous and level sensitive reset function. Figure 4-2 shows the timings to reset and reset-release for the power supply.

Figure 4-1 Reset signal connection example

Figure 4-2 Power-on reset release sequence

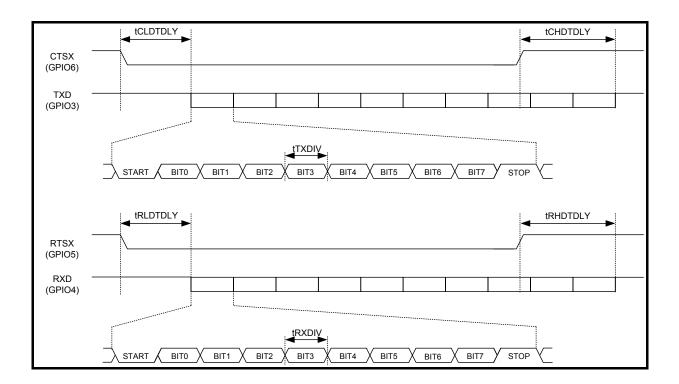

#### 4.2. UART Interface

#### 4.2.1. Features

TC35670FTG UART interface has the following features.

- 1.8 to 3.6 V operation

- Full-duplex start-stop synchronization data transfer (RX, TX)

- Selectable between 2-line start-stop synchronous transfer (Reception data and Transmission data) and 4-line start-stop synchronous transfer (Reception data, Transmission data, Reception flow control, and Transmission flow control).

- Start bit field(1 bit), Data bit field(8 bits LSB first), Stop bit field(1bit), No parity bit

- > UART transmit and receive data pins can be switched by the command of HCI mode. (UART2 function)

- > Programmable baud rate setting (9600 bps to 921.6 kbps) (Only 9600 bps is available for UART2.)

- > 12 (or more) character interval should be inserted between one transmission message and another transmission message.

The length of the interval can be changed by a command.

- > Error detection (character timeout, overrun error, framing error)

- Host wake-up function

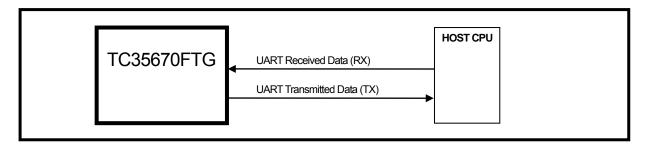

TC35670FTG communicates commands, status, and data with a host CPU through UART interfaces.

The UART interfaces are shared with GPIO pins. GPIO pins may functioned as a 2-wire system UART interface pins that are assigned by the Boot process after reset release. The UART interfaces can operate at 1.8 to 3.6 V depending on the VDDIO power supply voltage. Sharing the power supply pins with other hardware interfaces, they cannot operate at a different voltage from the one other hardware interfaces operate at.

Table 4-1 UART function summary

|       | PIN setting                                                                                                                                                        | Baud rate                                | Flow Control                                                                                    | Host wake-up                                                                             |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| UART1 | GPIO3: Transmitted data (TX)<br>GPIO4: Received data (RX)                                                                                                          | Default 115.2 kbps<br>9600 to 921.6 kbps | Disabled by default. GPIO5: Receive flow control (RTSX) GPIO6: Transmission flow control (CTSX) | Disabled by default. This function can be set to GPIO pins on the command. Default 10 ms |

| UART2 | Disabled by default. GPIO5: Transmitted data (TX) GPIO6: Received data (RX) *The UART2, it can be used in HCl mode, but can not be used simultaneously with UART1. | 9600 bps                                 | Unsupported                                                                                     | Unsupported                                                                              |

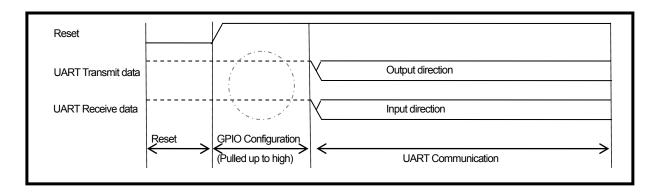

## 4.2.2. Connection Example

TC35670FTG UART can be connected with an UART interface on a host MCU. Figure 4-3 shows two-wire start-stop synchronization data transfer (RX, TX) connection example with an external host CPU. The timing chart to assign the GPIO pins to the UART function is shown in Figure 4-4.

Figure 4-3 UART connection example

Figure 4-4 UART function assignment

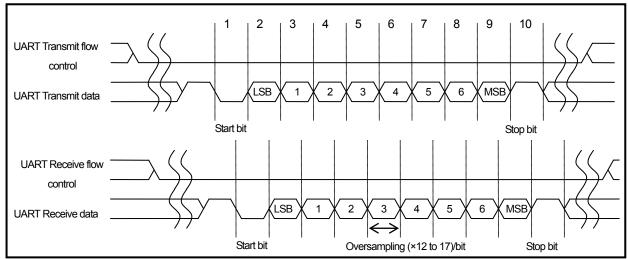

#### 4.2.3. Frame Format

TC35670FTG supports the following format.

Number of data bits: 8 bits (LSB first)

Parity bit: no parity

Stop bit: 1 stop bit

Flow control: RTSX/CTSX NOTE: Flow control is enabled only possible for UART1 in command.

Figure 4-5 shows UART data frame.

Figure 4-5 UART data frame

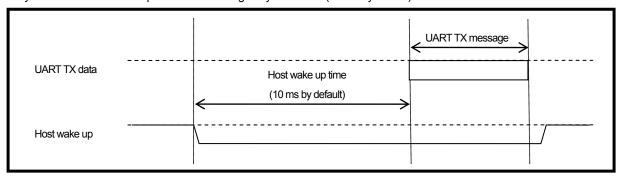

## 4.2.4. Host Wake up Function

TC35670FTG can wakes up its host before sending UART data to the host. This function is disabled by default, but can be assigned to GPIO by command. Host wake up time can be changed by command (10 ms by default).

Figure 4-6 Host wake up

#### 4.2.5. HCI mode

When TC35670FTG is used in the HCI mode, UART is the host interface to receive HCI commands.

The Bluetooth® wireless performance can be tested in HCI mode by the measurement equipment which connects the UART directly.

#### 4.2.5.1. HCI Reset

Sends a HCI reset command from the host, at least  $150\mu s$  from the command complete event can be processed the following command successfully.

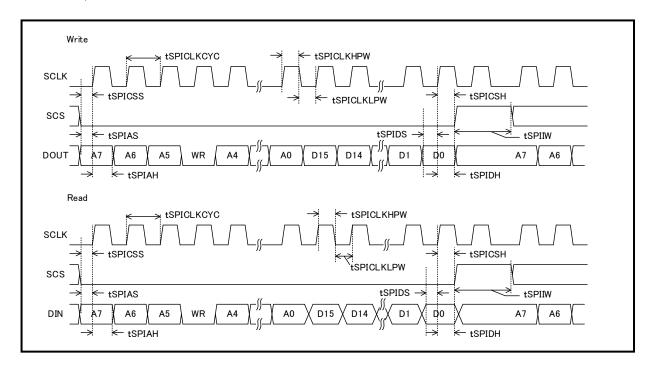

#### 4.3. SPI Interface

#### 4.3.1. Features

TC35670FTG has the following main features for a serial memory interface

Operation voltage: 1.8 to 3.6 V

SPI interface

Chip select: 1 channel

Chip select polarity: High-active, Low-active

> Serial clock master operation: Polarity and phase are adjustable (one out of four options can be selectable)

Serial clock frequency: 25 kHz to 6.5 MHz

Serial data transfer mode: MSB-first, LSB-first

SPI interface can operate at 1.8 to 3.6 V depending on VDDIO, however, cannot operate at different voltage from ones other interfaces are operate at.

## 4.3.2. Connection Example

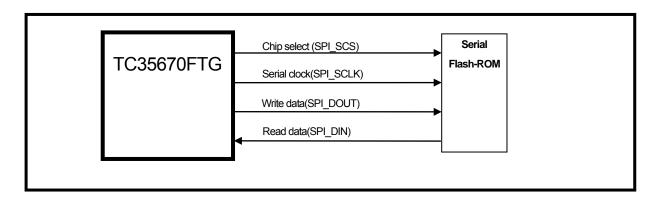

Serial EEPROMs and serial Flash-ROMs can be connected to TC35670FTG SPI interface.

TC35670FTG has one chip select port. Figure 4-7 shows a connection example, where a serial Flash-ROM is connected to TC35670FTG.

Figure 4-7 Connection example for serial Flash-ROM using SPI interface

## 4.4. I<sup>2</sup>C Interface

#### 4.4.1. Features

TC35670FTG has the following main features for a serial memory interface.

Operation voltage: 1.8 to 3.6 V

> I<sup>2</sup>C bus interface

✓ Operation mode: I<sup>2</sup>C bus master

✓ Serial clock frequency: Standard mode (Max 100 kHz), Fast mode (Min100 kHz to Max 400 kHz)

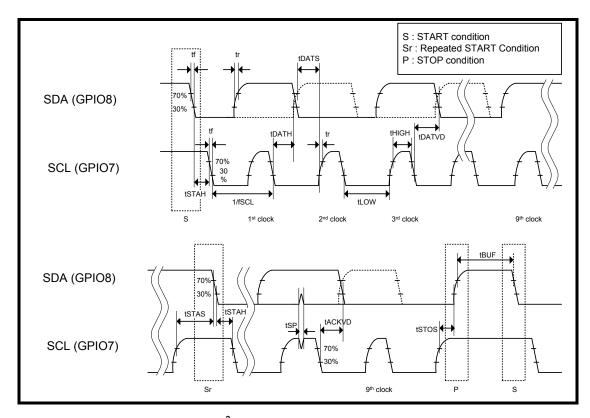

✓ Output mode: Open-drain output, CMOS output

✓ Device address format: 7 bits address (10 bits address is not supported)

I<sup>2</sup>C interface can operate at 1.8 to 3.6 V depending on VDDIO, however, cannot operate at different voltage from ones other interfaces are operate at.

## 4.4.2. Connection Example

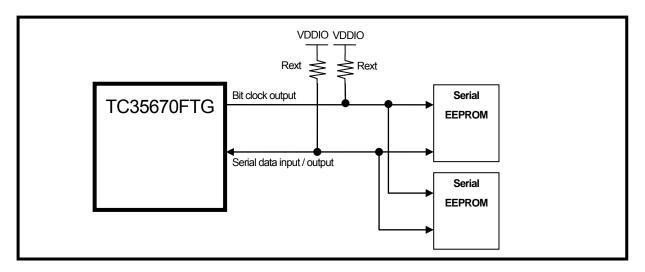

Figure 4-8 shows a connection example of a serial EEPROM using  $I^2C$  bus interface of the open-drain mode. External pull-up resistors (Rext) are necessary for both serial clock line and serial data line.

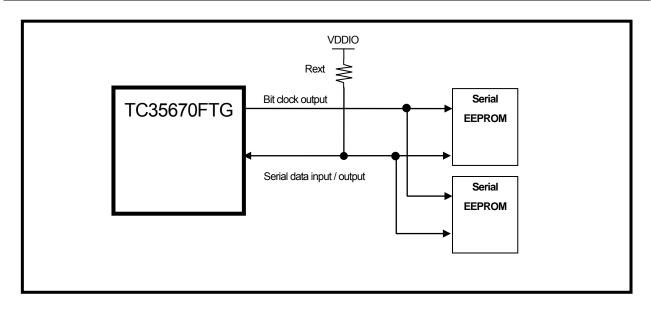

Figure 4-9 shows another connection example where  $I^2C$  bus is in the CMOS output mode. Only the serial data line needs Rext because this line can be driven by neither TC35670FTG nor a serial EEPROM.

Figure 4-8 Connection example for serial EEPROM with I<sup>2</sup>C-bus interface (Open-drain output)

Figure 4-9 Connection example for serial EEPROM with I<sup>2</sup>C-bus interface (CMOS output)

#### 4.5. PWM Interface

TC35670FTG has a PWM interface that can be used for LED, buzzer control, etc.

The PWM interface has the following features.

- > Arbitrary pulse generation function

- It can select the source clock from 13 MHz and 32.768 kHz

- It has 12 bits clock division setting up to 1/4096: 8 Hz to 16.384 kHz (32.768 kHz), 3.17 kHz to 6.5 MHz (13 MHz)

- It can mask the pulse output on the basis of 50 ms (rhythm function)

- > The interrupt can be generated in synchronization with the cycle of 1s rhythm pattern.

- > It can switch the pulse output to Low / High active

- > Duty of the pulse output is adjustable.

#### 4.5.1. Pulse Generation Function

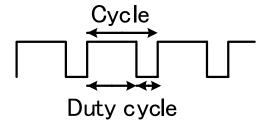

Figure 4-10 shows a brief explanation of the pulse generation. TC35670FTG can adjust output pulse frequency by changing its cycle. Also it can adjust on/off ratio by changing its duty.

The cycle (frequency) can be set from 8 Hz to 16.384 kHz for 32.768 kHz clock, and from 3.17 kHz to 6.5 MHz for 13 MHz clock. The duty can be set from 0% to 100%

Figure 4-10 PWM pulse generation function

## 4.5.2. Rhythm Function (Output Masking)

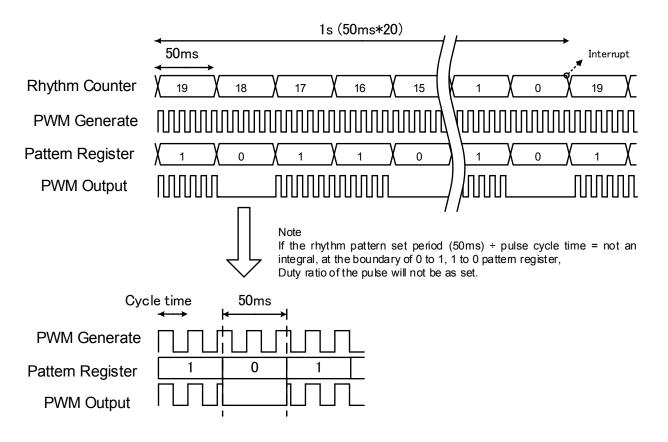

Figure 4-11 shows the brief explanation of PWM rhythm function. In addition to the one for pulse generation, TC35670FTG has another timer that has  $50 \text{ ms} \times 20 = 1 \text{s}$  (rhythm counter). That timer has 20 bits register (pattern register), each bit corresponds to the rhythm counter that counts down in every 50 ms. When the pattern register is zero, the PWM output is masked to zero or one. Using this function, LED or buzzer can be on with 1s periodical pattern

Figure 4-11 PWM Rhythm Function

#### 4.6. ADC

#### 4.6.1. Features

TC35670FTG has 3 channels of 10 bits ADCs for battery monitoring, analog inputs from external sensors, for example. The ADC has the following features.

- 2 channels for analog inputs (shared with GPIO pins)

- 1 channel for VDD voltage monitor

The reference input is connected to VDD, and the analog input is to built-in LDO output 1.1V.

Please refer to 4.6.2 for how to calculate VDD absolute value.

Maximum conversion rate: 1 MS/s

#### 4.6.2. Descriptions

The ADC has 10 bits conversion accuracy and can work for input voltages from 0 V to 3.6 V (VDD). It has 3 channels of analog inputs. And the channel 0 is connected to LDO output 1.1V. And the channels 1 to 2 are shared with GPIO pins.

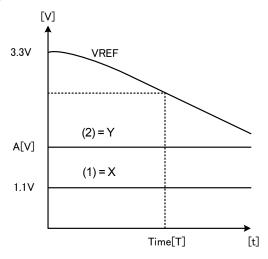

When a battery is used as power source, the reference voltage can slide over time because the battery is connected as reference voltage. In that case, the LDO output voltage connected to Channel 0 can be used as a reference voltage. So the input voltage to Channel 1 or Channel 2 is converted by the reference voltage of Channel 0 and the converted value is used to calculate a correct digital value by the CPU. The following shows the conversion method of the input voltage.

Voltage A at time T can be calculated as follows

- (1) LDO 1.1V is AD converted. This is X.

- (2) Voltage A is AD converted. This is Y

- (3) Assuming absolute value of voltage A is Z, 1.1:X = Z:Y

$$Z[V] = 1.1 \times Y/X$$

Calculation example:

Suppose 1.1V LDO output at ch0 is converted to 0x0188, and measurement target at ch1 0x0134, the absolute voltage at ch1 Z [v] is given by  $1.1 \times 0x0188 / 0x0134 = 1.1 \times 392 / 308 = 1.4$  [V].

Figure 4-12 shows conceptual of voltage conversion.

Figure 4-12 Voltage conversion concep

The ADC converts inputs from channels selected by register settings. When a conversion has finished, the CPU detects it by the interrupt or register polling, and then returns the results. The maximum sampling rate depends on software load on the CPU.

#### 4.7. IC Reference Clock Interface

#### **4.7.1.** Features

TC35670FTG has the following features for IC reference clock interface which receives an external clock.

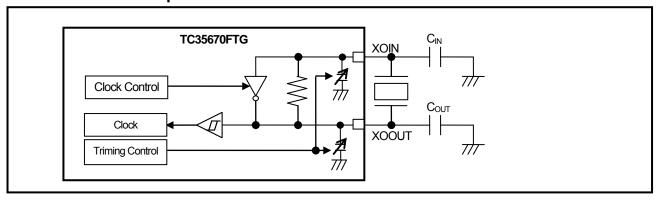

Clock frequency: 26 MHz (The deviation should be adjusted within 50 ppm at the temperature in use)

TC35670FTG has an internal feed-back resistor between XOIN and XOOUT and doesn't require external feedback resistors. Please adjust external capacitors ( $C_{IN}$  and  $C_{OUT}$ ) based on PCB layout and assembly if necessary within the range of the X'tai's specification.

## 4.7.2. Connection Example

Figure 4-13 Crystal oscillator connection example

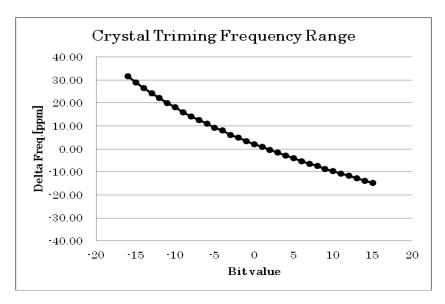

## 4.7.3. Oscillation Frequency Adjust Function

Crystal OSC circuit has a capacitor array inside, and the OSC frequency can be trimmed by a register bit value from 0 to 31. Figure 4-14 shows an example of the adjusted frequency measured with our test board using 26 MHz Crystal. This characteristic can vary depending on the crystal itself, external capacitors, resistors and PCB patterns.

Figure 4-14 Trimming frequency range example

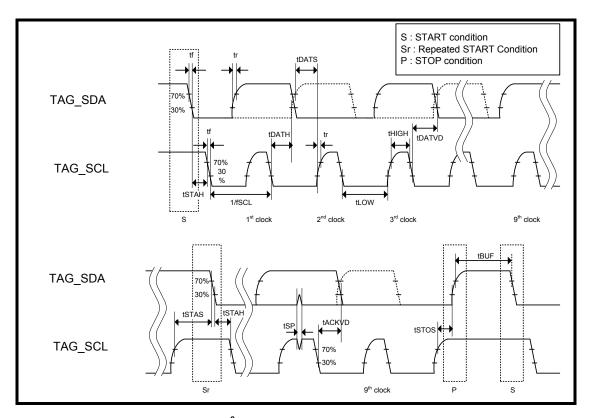

#### 4.8. TAG- wireless interface

TC35670FTG has a NFC Forum Type 3 Tag (NFC Tag) function built-in, which is equipped with FeliCa contactless IC card technology. NFC Tag provides non-volatile memory (EEPROM), wireless interface which conforms to NFC Forum Type 3 Tag standards, and wired interface by  $l^2$ C.

This section will explain a wireless interface of NFC tag.

#### 4.8.1. Features

Table 4-2 shows propagation performace of TAG wireless interface.

Table 4-2 Transmission characteristic of the wireless interface

| Item                     | Remarks                                 |

|--------------------------|-----------------------------------------|

| Data transmission format | Half duplex, Synchronization            |

| Carrier frequency (fc)   | 13.56 MHz                               |

| Modulation method        | ASK                                     |

| Bit coding               | Manchester code, MSB First              |

| Data transmission speed  | 212 kbps/424 kbps (Automatic detection) |

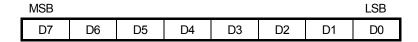

#### 4.8.2. Character format

Figure 4-15 shows character format. The character consists of 8 bits data. There is no start bit, no stop bit, and no parity. Character is transmitted MSB first. Multiple characters are successively transferred. There is no space between characters.

Figure 4-15 Character format

#### 4.8.3. Frame format

Figure 4-16 shows frame format. The frame consists of multiple characters. Sync code, LEN, packet data, and CRC fields are defined within the frame.

Packet is the addition of preamble (6bytes 00h) and frame. Data is communicated to wireless reader/writer by packet unit. Packet received by TC35670FTG is a command. Packet transmitted by TC35670FTG is a response. Table 4-3 shows field definition of packet.

| (2bytes)  | (1byte) | (n bytes)   | (2 bytes) |

|-----------|---------|-------------|-----------|

| Sync code | LEN     | Packet data | CRC       |

Figure 4-16 Frame format

Table 4-3 Field definition of packet

| Field name       | Byte length | Definition                                                                 |

|------------------|-------------|----------------------------------------------------------------------------|

| Preamble         | 6           | 00h 00h 00h 00h 00h                                                        |

| Sync code        | 2           | B2h 4Dh                                                                    |

| LEN(data length) | 1           | Value of n+1                                                               |

| Packet data      | n           | Packet data of command or response                                         |

| CRC              | 2           | Check sum by CRC-CCITT of data length and packet data                      |

|                  |             | (Big endian)                                                               |

|                  |             | Initial value: 00h 00h                                                     |

|                  |             | Generating polynomial: X <sup>16</sup> +X <sup>12</sup> +X <sup>5</sup> +1 |

Command packet data consists of command code (top 1 byte) and command data. Command code is a code which identifies command type.

| (1 Byte)     | (n-1Byte)    |

|--------------|--------------|

| Command code | Command data |

Figure 4-17 packet data of command

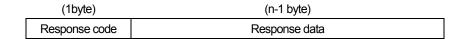

Packet data of response consists of response code (top 1 byte) and response data. Response code is a code which recognizes response type.

Figure 4-18 Packet data of response

## 4.8.4. Command type

Table 4-4 shows commands which TC35670FTG supports.

Table 4-4 Command type

| Command name             | Command code value | Response code value | Functional outline                              |

|--------------------------|--------------------|---------------------|-------------------------------------------------|

| Polling                  | 00h                | 01h                 | Command by which wireless read/writer catches / |

|                          |                    |                     | identifies TC35670FTG                           |

| Read Without Encryption  | 06h                | 07h                 | Reading block data                              |

| Write Without Encryption | 08h                | 09h                 | Writing block data                              |

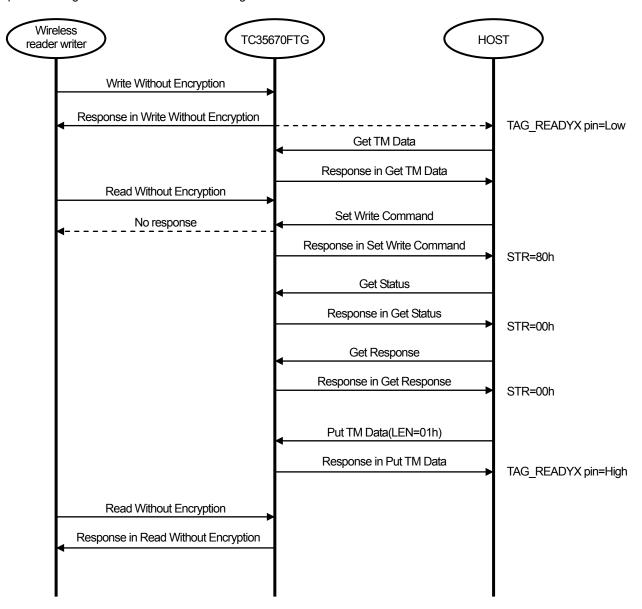

## 4.8.5. Operation sequence

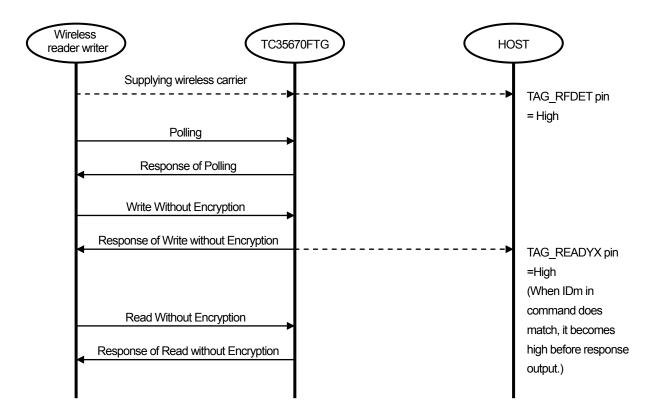

If wireless carrier is detected, TAG\_RFDET pin outputs high level. If wireless carrier disappears, it turns back to low level due to pull-down resistance. VDDIO and VDD pin needs power supply for TAG\_RFDET pin to output high.

At Write without Encryption or Read without Encryption, if IDm stored in TC35670FTG and iDm with command are consistent, TAG\_READYX pin outputs high level. After that, during supply of internal power source, the high is kept. VDDIO and VDD pin needs power supply for TAG\_READYX pin to output high.

By becoming high in TAG READYX pin, HOST can get to know that wireless reader writer accesses TC35670FTG.

Figure 4-19 Sequence example of operation over the wireless interface

#### 4.8.6. Warning

- ① At the period which is from reading WCNT value to writing with MAC, commands of wired interface execute and WCNT may change. In this case, at the execution of Write without Encryption, WCNT value is changed. Therefore, in case of writing with MAC, error of inconsistency of MAC value occurs. If this error occurs, read WCNT value again and then write with MAC. Or, before reading WCNT value, set to prohibit Set Write Command of the wired interface by using WLOCK block.

- ② During the execution of wired interface command, receiving commands of wireless interface are ignored and no response to the wireless reader writer is made (no response). In this case, resend commands from the wireless reader writer.

- ③ In case that TC35670FTG prohibits Write without Encryption by using WLOCK block, TC35670FTG does not make a response to Write Without Encryption. In this case, resend commands to the wireless reader writer until Write Without Encryption is permitted in wired interface side.

- The TAG\_RECTOUT pin can be used to optimize the value of the condenser between the TAG\_L0 pin and the TAG\_L1 pin. The output voltage of the TAG\_RECTOUT pin should be monitored. The wireless reader and writer should not be close to the pin. The higher output voltage is monitored when the resonance condenser value is closer to the optimized value.

## 4.9. TAG Wire Interface

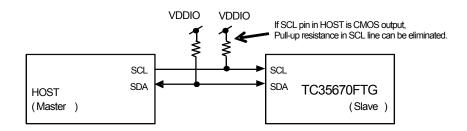

TC35670FTG has the I<sup>2</sup>C interface which operates as the TAG-dedicated slave (TAG-I<sup>2</sup>C interface). The features of the TAG-I<sup>2</sup>C mode are as follows:

#### 4.9.1. Features

- 7 bits address capability, slave operating

- Serial clock frequency: 400 kHz(max)

- > Slave address value is set in EEPROM (UC block).

- Error detection function(Redundancy Code (RC) error is detected)

## 4.9.2. Connection Example

The connection to the host in the TAG-I<sup>2</sup>C mode is shown in Figure 4-20. Serial clock (SCL) and Data (SDA) line are connected to pull-up resistances. If SCL pin in HOST is CMOS output, only SDA line should be connected to the pull-up resistance. To decide pull-up values, refer to the electric characteristics and the datasheet of the host.

Figure 4-20 Connection example in usage of TAG-I<sup>2</sup>C mode

## 4.9.3. Operation explanation

When TAG-I<sup>2</sup>C detects start condition, it receives 7 bits slave address of top character and W/R selection. If slave address stored in UC block and received slave address are consistent, TAG-I<sup>2</sup>C outputs ACK. If W is selected in the W/R selection, TAG-I<sup>2</sup>C prepares for received commands since then. TAG-I<sup>2</sup>C outputs ACK every received character. If R is selected in the W/R selection, TAG-I<sup>2</sup>C prepares for sending responses since then. Every sent character, TAG-I<sup>2</sup>C checks ACK or NACK which HOST outputs. If TAG-I<sup>2</sup>C detects stop condition, it completes receiving commands.

If slave address of top character is inconstant with slave address stored in UC block, TAG- $I^2$ C G does not output ACK. In this time, if W is selected in the W/R selection, TAG- $I^2$ C ignores receiving commands since then and does not output ACK. If R is selected in the W/R selection, TAG- $I^2$ C ignores transmission requests of response since then and does not output data. When stop condition is detected, TAG- $I^2$ C moves to the status of waiting start condition again.

After receiving commands, TAG-I<sup>2</sup>C becomes status of waiting of sending responses. If received top character is W selection in this condition, TAG-I<sup>2</sup>C outputs ACK to top character. However it ignores receiving commands since then and does not output ACK. If top character is R selection, TAG-I<sup>2</sup>C outputs ACK and prepares for sending responses since then. TAG-I<sup>2</sup>C checks ACK or NACK which is output from HOST every sent character. However, if NACK is detected, it stops sending. If SCL is input after NACK, TAG-I<sup>2</sup>C outputs FFh. If TAG-I<sup>2</sup>C detects stop condition, it completes receiving commands.

If strat condition is detected (no stop condition) in the middle of commands, response or character, TAG-I<sup>2</sup>C interrupts receiving or sending process and moves to status of waiting of receiving top character (7 bits slave address and W/R selection) Stop bit is detected in the middle of commands or response, TAG-I<sup>2</sup>C interrupts receiving or sending process and moves to status of waiting of receiving top character (7 bits slave address and W/R selection).

$\ln l^2 C$  mode, TAG- $l^2 C$  is not capable of general call address and 10 bits slave address assignment. And, TAG- $l^2 C$  never outputs low level to TAG SCL pin (clock stretch).

## 4.9.4. Frame format

Figure 4-21 shows frame format. The frame consists of multiple characters. Fields such as SYN, CMD/STR, Payload, and RC are defined in the frame.

| (1 byte) | (1 byte) | (0 to 230 bytes) | (1 byte) |

|----------|----------|------------------|----------|

| SYN      | CMD/STR  | Payload          | RC       |

Figure 4-21 Frame format

Frame is used as packet and data is communicated to wire reader writer by packet unit. Packet which TC35670FTG receives is a command. Packet which TC35670FTG sends is a response. Table 4-5 shows definition of packet field.

Table 4-5 Packet field definition

| Field name | Byte     | Definition                                                                          |

|------------|----------|-------------------------------------------------------------------------------------|

|            | length   |                                                                                     |

| SYN        | 1        | Sync code                                                                           |

|            |          | (In case of I <sup>2</sup> C, 7 bits slave address and W/R selection (W: command R: |

|            |          | Response) is specified to SYN. Wire reader-writer outputs SYN of response.)         |

|            |          | (In case of SPI/UART, 80h is specified as sync code.)                               |

| CMD/STR    | 1        | CMD: Command assignment                                                             |

|            |          | STR: Response status                                                                |

| Payload    | 0 to 230 | Command/ response dependable                                                        |

| RC         | 1        | Check sum                                                                           |

|            |          | (Exclusive OR between CMD/STR , Payload and FFh)                                    |

# 4.9.5. Command type

Table 4-6 shows commands which TC35670FTG supports. Type of commands is specified with CMD.

Table 4-6 Command type

| Command name      | Value of CMD | Outline of function                                                      |

|-------------------|--------------|--------------------------------------------------------------------------|

| Set Write Command | 01h          | Stating the execution of Write without Encryption (wireless interface    |

|                   |              | receiving invalid)                                                       |

| Set Read Command  | 02h          | Starting of the execution of Read without Encryption (wireless interface |

|                   |              | receiving invalid)                                                       |

| Get Status        | 03h          | Obtaining status                                                         |

| Get Length        | 04h          | Obtaining data length of execution result                                |

| Get Response      | 05h          | Obtaining an execution result (Wireless interface receiving valid)       |

| Get TM Data       | 07h          | Obtaining data in Through mode                                           |

| Put TM Data       | 08h          | Setting data in Through mode (Wireless interface receiving valid)        |

STR which is included in response indicates status for command. Table 4-7 shows the content of STR. Value of STR might be OR between higher 4 bits and lower 4 bits.

Table 4-7 Content of STR

| Value of STR | content in status                        |

|--------------|------------------------------------------|

| 8Xh          | In process of wired interface command    |

| 4Xh          | In process of wireless interface command |

| 1Xh          | Presence of Through mode data            |

| X8h          | Framing error ( only UART mode)          |

| X4h          | Abnormality in condition of command      |

|              | execution                                |

| X2h          | Value of CMD is not defined.             |

| X1h          | RC abnormality                           |

| 00h          | No information ( Command processing      |

|              | completion)                              |

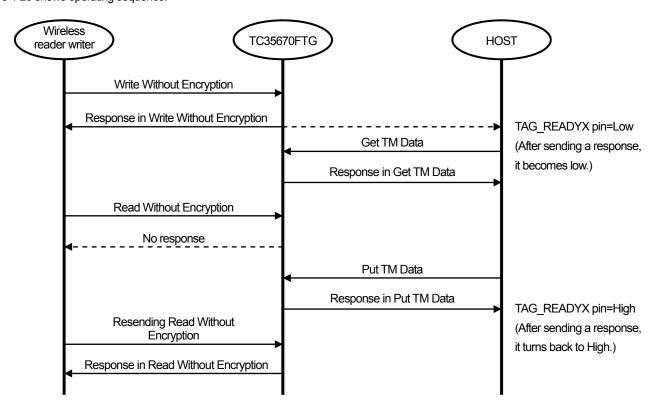

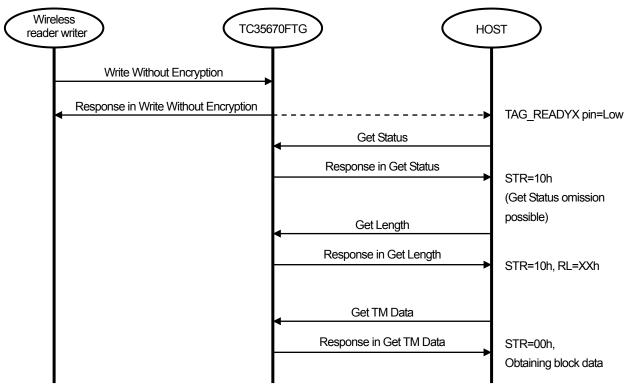

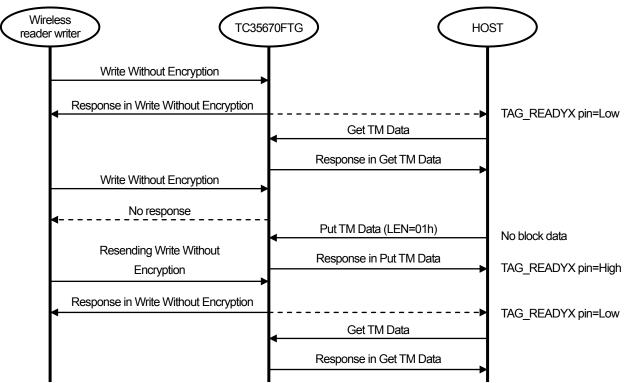

## 4.9.6. Operation Sequence

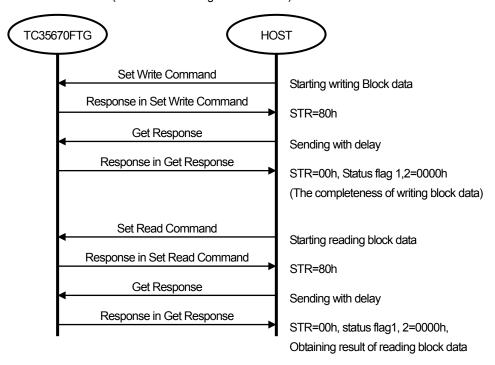

• Operating sequence of wired interface(Get Status/Get Length are not used.)

Figure 4-22 Operating sequence over the wired interface(Get Status/Get Length are not used)

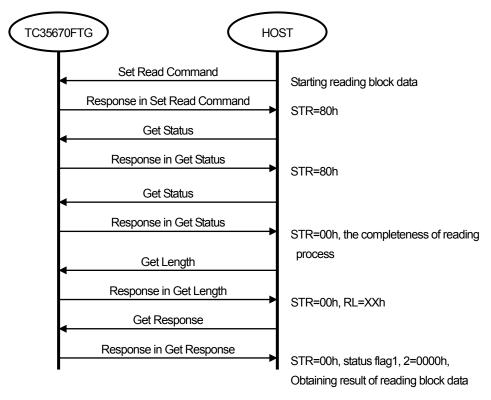

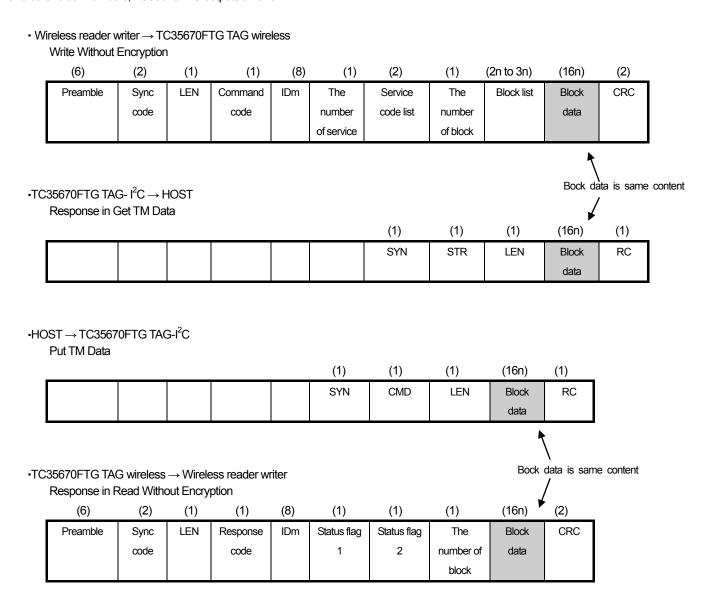

Operating sequence of wired interface (Get Status/Get Length are used)

Figure 4-23 Operating sequence over the wired interface (Get Status/Get Length are used)

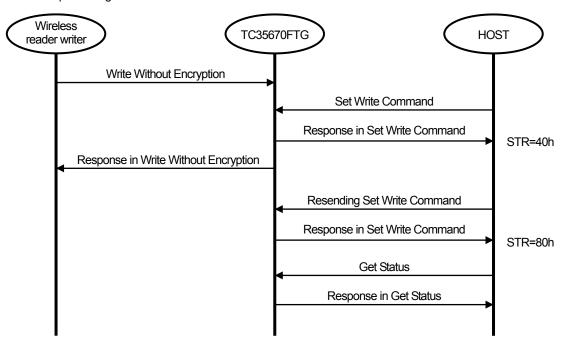

Command processing of wireless interface

Figure 4-24 Command processing sequence of wireless interface

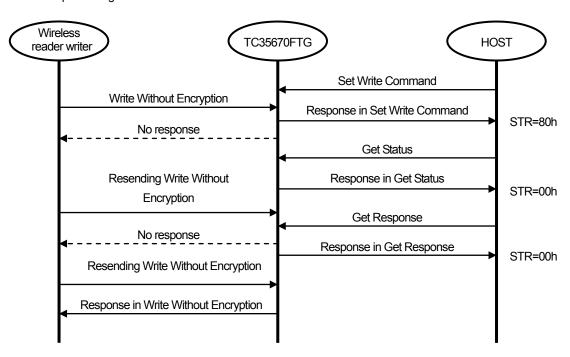

Command processing of wired interface

Figure 4-25 command processing sequence of wired interface

## **4.9.7.** Warning

- ① In case that, in I<sup>2</sup>C mode, many SCL K is input and response which is longer than command assignment is requested, TC35670FTG outputs FFh.

- ② Even if excessive data is received after RC, if RC is correct, TC35670FTG processes commands.

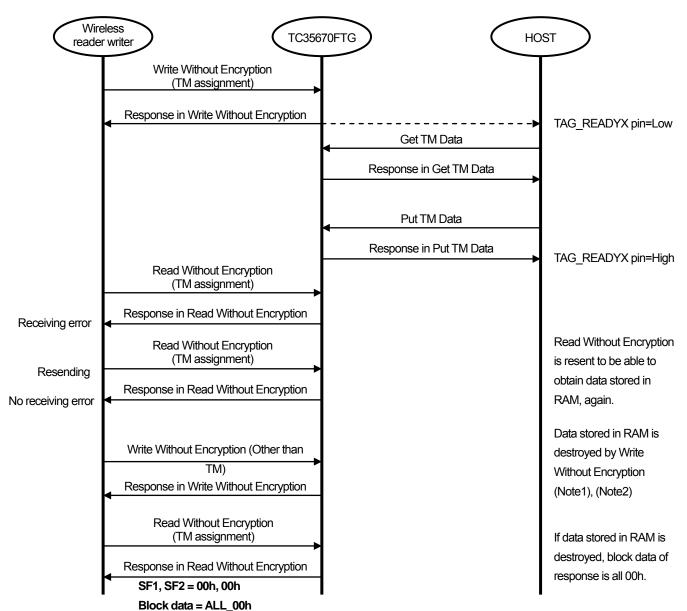

- ③ If STR in the Response for Get Response is 00h (Command procedure completes), at the response of Get Response, do not resend Get Response. STR of response at resending is 04h. To obtain the result of command process again, try again from Set Write Command /Set Read Command