# Product Document

## **AS7000**

#### **Biosensor**

## **General Description**

The AS7000 device provides a flexible analog front end for light sensing applications. The photodiode input circuit can be configured in different ways to guarantee best tradeoff between speed and sensitivity for a large number of different sensing applications.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits and Features**

The benefits and features of AS7000, Biosensor are listed below:

Figure 1: Added Value of Using AS7000

| Benefits                                                          | Features                                                                                                        |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Allows smallest application size e.g. narrow HRM measurement band | <ul> <li>Single device integrated optical solution</li> <li>Integrated 32bit Cortex-M0 processor</li> </ul>     |

| Good HRM measurement quality                                      | Low noise analog optical front end                                                                              |

| Additional information for end user                               | Analog electrical front end (e.g. for NTC or GSR)                                                               |

| Long operating time                                               | <ul> <li>Hardware sequencer to offload processor</li> <li>Adjustable LED driver with current control</li> </ul> |

| Works reliably with ambient light                                 | Synchronous detector                                                                                            |

## **Applications**

The device is suitable for optical sensor platform.

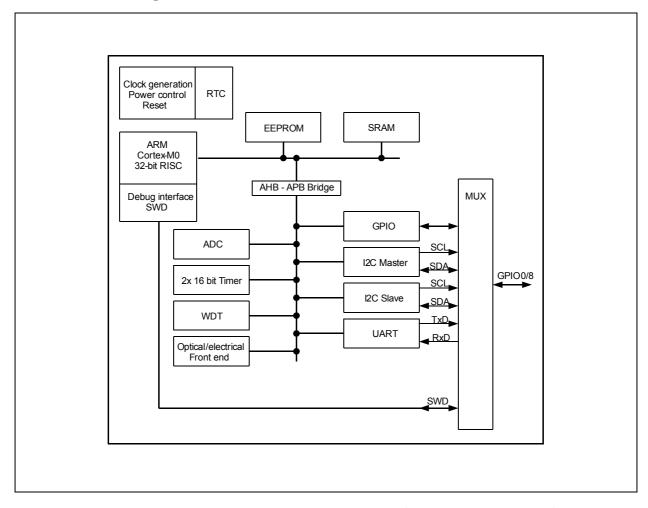

## **Block Diagram**

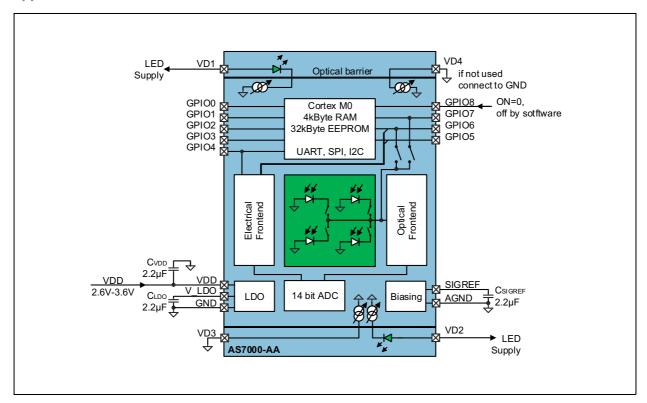

The functional blocks of this device are shown below:

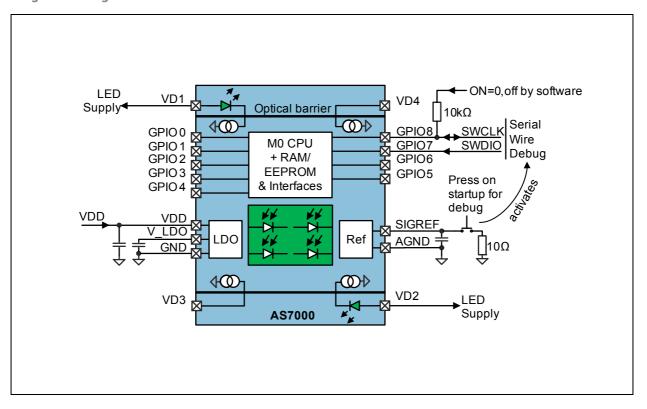

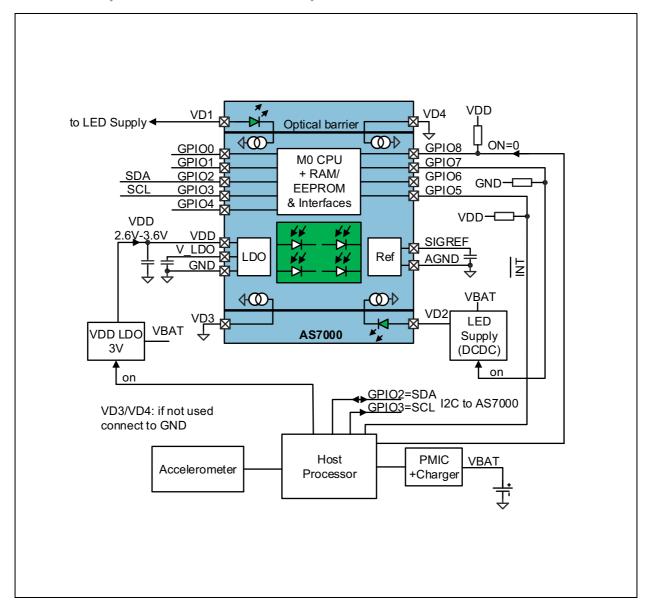

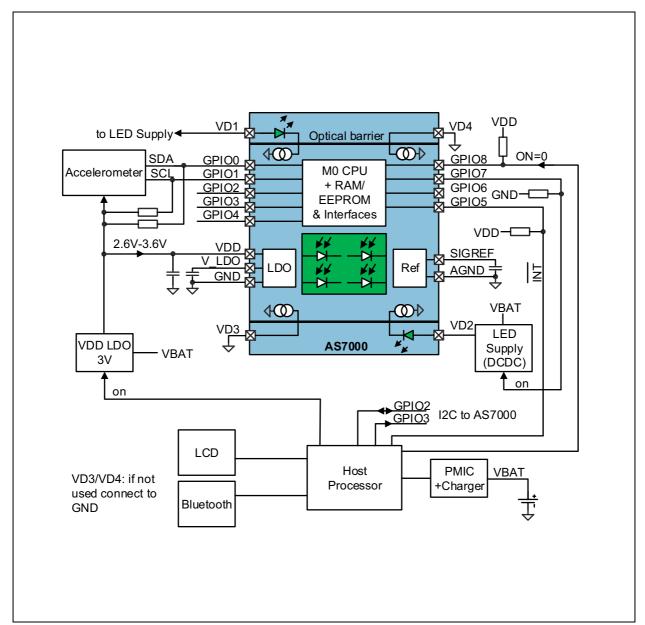

Figure 2: Application Schematic AS7000-AA

Page 2ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

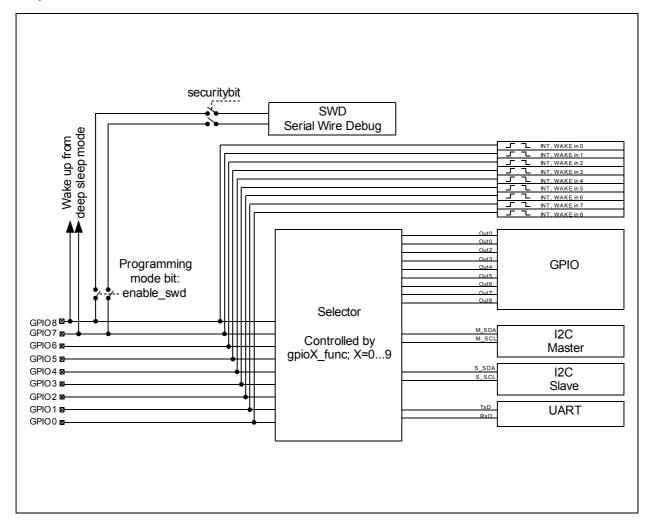

## **Pin Assignments**

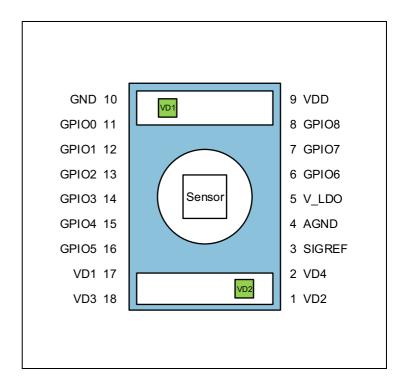

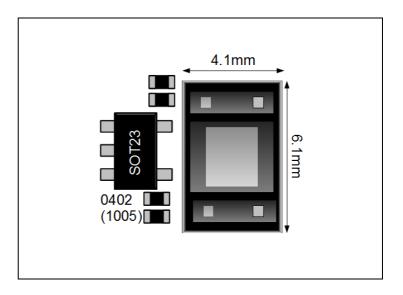

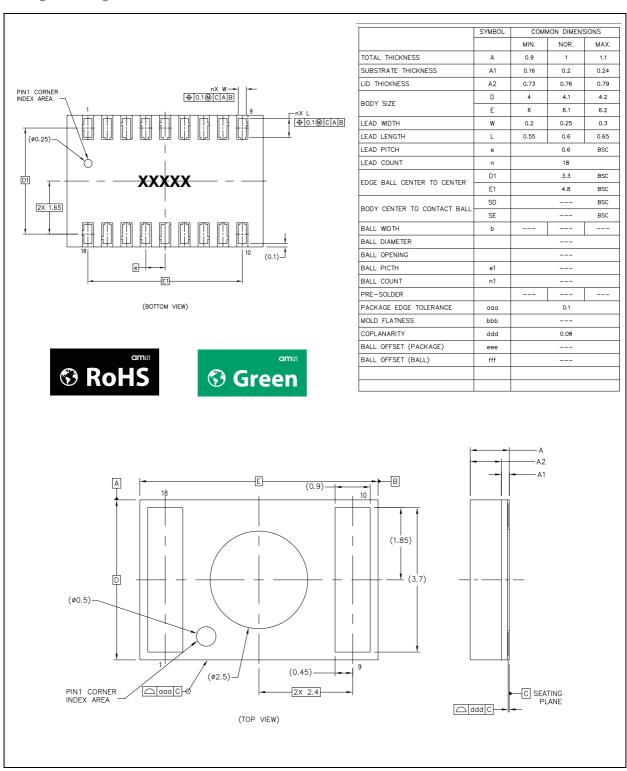

Figure 3:

Optical Module Pinout (Top View) – AS7000-AA

## **Optical Module Pinout:**

This drawing is not to scale

Figure 4: Pin Description

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VD2      | Supply voltage for LED D2 – connect unused current sinks to GND                                                                                                                                                                                                            |

| 2          | VD4      | Supply voltage for LED D4 – connect unused current sinks to GND                                                                                                                                                                                                            |

| 3          | SIGREF   | Analog reference output. Connect 2.2 $\mu$ F capacitor to GND (e.g. 0402 sized capacitor GRM153R60J225ME95 from Murata – needs to have >1 $\mu$ F specified for 1.0V voltage bias); do not load externally The typical operating voltage on this pin is 0.6V (sigref_en=1) |

| 4          | AGND     | Analog ground. Connect to low noise GND                                                                                                                                                                                                                                    |

| 5          | V_LDO    | 1.9V output voltage. Connect 2.2µF capacitor to GND (e.g. 0402 sized capacitor GRM153R60J225ME95 from Murata – needs to have >1µF with 1.0V voltage bias); do not load externally                                                                                          |

| 6          | GPIO6    | General purpose input/output                                                                                                                                                                                                                                               |

| 7          | GPIO7    | General purpose input/output                                                                                                                                                                                                                                               |

| 8          | GPIO8    | General purpose input/output                                                                                                                                                                                                                                               |

| 9          | VDD      | Supply voltage.                                                                                                                                                                                                                                                            |

| 10         | GND      | Power supply ground. All voltages are referenced to GND.                                                                                                                                                                                                                   |

ams Datasheet Page 3

[v1-12] 2018-Feb-26 Document Feedback

| Pin Number | Pin Name | Description                                                     |

|------------|----------|-----------------------------------------------------------------|

| 11         | GPIO0    | General purpose input/output                                    |

| 12         | GPIO1    | General purpose input/output                                    |

| 13         | GPIO2    | General purpose input/output                                    |

| 14         | GPIO3    | General purpose input/output                                    |

| 15         | GPIO4    | General purpose input/output                                    |

| 16         | GPIO5    | General purpose input/output                                    |

| 17         | VD1      | Supply voltage for LED D1 – connect unused current sinks to GND |

| 18         | VD3      | Supply voltage for LED D3 – connect unused current sinks to GND |

Page 4ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

## **Absolute Maximum Ratings**

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings<sup>(1)</sup>

| Symbol                | Parameter                                                          | Min  | Max                      | Units | Comments                                           |  |  |  |

|-----------------------|--------------------------------------------------------------------|------|--------------------------|-------|----------------------------------------------------|--|--|--|

|                       | Electrical Parameters                                              |      |                          |       |                                                    |  |  |  |

| VDD                   | Supply voltage to ground                                           |      | 3.63V                    | V     |                                                    |  |  |  |

| V_LDO                 | Supply voltage to ground                                           |      | 1.98V max.<br>VDD+0.3V   | V     |                                                    |  |  |  |

| V <sub>IN</sub>       | Input pin voltage to<br>ground, all pins except<br>VD1/VD2/VD3/VD4 | -0.3 | VDD+0.3V<br>max. 3.8V    | V     |                                                    |  |  |  |

| V <sub>IN-VD1-4</sub> | Input pin voltage to<br>ground, pins<br>VD1/VD2/VD3/VD4            | -0.3 | 5.5                      | V     |                                                    |  |  |  |

| V <sub>INLDO</sub>    | Input pin voltage to ground, pin SIGREF                            | -0.3 | V_LDO+0.3V<br>max. 1.98V | V     |                                                    |  |  |  |

| I <sub>SCR</sub>      | Input current<br>(latch-up immunity)                               | -100 | 100                      | mA    | JEDEC JESD78                                       |  |  |  |

|                       | Electrostatic Discharge                                            |      |                          |       |                                                    |  |  |  |

| ESD <sub>HBM</sub>    | All pins except<br>VD1/VD2/VD3 and VD4                             | ±1.0 |                          | kV    | Electrostatic discharge HBM:<br>JEDEC JESD22-A114F |  |  |  |

|                       | Pins VD1/VD2/VD3 and VD4                                           |      | ±350                     | V     | JEDEC JEDDZZ ATTAI                                 |  |  |  |

ams Datasheet Page 5

[v1-12] 2018-Feb-26 Document Feedback

| Symbol            | Parameter                                 | Min | Max | Units | Comments                                                                                                                                                                                                                    |  |  |  |  |

|-------------------|-------------------------------------------|-----|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   | Temperature Ranges and Storage Conditions |     |     |       |                                                                                                                                                                                                                             |  |  |  |  |

| T <sub>AMB</sub>  | Operating temperature                     | -30 | 70  | °C    |                                                                                                                                                                                                                             |  |  |  |  |

| T <sub>STRG</sub> | Storage temperature range                 | -40 | 85  | °C    |                                                                                                                                                                                                                             |  |  |  |  |

| T <sub>BODY</sub> | Package body temperature                  |     | 260 | °C    | IPC/JEDEC J-STD-020 The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." |  |  |  |  |

| RH <sub>NC</sub>  | Relative humidity non-condensing          | 5   | 85  | %     |                                                                                                                                                                                                                             |  |  |  |  |

| MSL               | Moisture sensitivity level                | 3   |     |       | Maximum floor life time of 168h                                                                                                                                                                                             |  |  |  |  |

#### Note(s):

1. All optical customer designs shall be reviewed by  ${\bf ams}$  before production.

Page 6ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

## **Electrical Characteristics**

VDD=2.6 to 3.6V, typ. values are at  $T_{AMB}$ =25°C (unless otherwise specified).

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Operating Conditions

| Symbol           | Parameter                           | Conditions                                                                                   | Min | Тур | Max        | Unit |

|------------------|-------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|------------|------|

| VDD              | Supply voltage                      |                                                                                              | 2.6 | 3.3 | 3.6        | V    |

| VLED             | LED Supply voltage                  | VD1, VD2, VD3, VD4 if a<br>LED is used                                                       |     |     | 5.0        | V    |

| V <sub>LDO</sub> | LDO voltage, generated by<br>AS7000 | Pin V_LDO                                                                                    |     | 1.9 |            | V    |

| T <sub>AMB</sub> | Operating free-air temperature      |                                                                                              | -30 |     | 70         | °C   |

|                  |                                     | CPU + EEPROM running at<br>16MHz;<br>from 1.8V supply; all<br>periphery blocks off           |     | 1.4 |            | mA   |

|                  |                                     | CPU in sleep mode,<br>16MHz oscillator running;<br>all periphery blocks off                  |     | 360 |            | μΑ   |

|                  | Supply current                      | ADC 14bit; only during conversion                                                            |     | 2   |            | mA   |

|                  |                                     | Photodiode amplifier and<br>Optical front end                                                |     | 430 |            | μΑ   |

| IDD              |                                     | Electrical front end                                                                         |     | 180 |            | μΑ   |

|                  |                                     | LED current sink per<br>channel 25mA range                                                   |     | 210 |            | μΑ   |

|                  |                                     | LED current sink per<br>channel 50mA and<br>100mA range                                      |     | 340 |            | μΑ   |

|                  |                                     | Deep sleep mode (1), (2)<br>512Hz oscillator running,<br>LDO operating, processor<br>powered |     | 25  |            | μΑ   |

|                  |                                     | Power down <sup>(3)</sup><br>GPIO8=VDD.                                                      |     | 0.8 |            | μΑ   |

| VOL              | GPIO0-8 output low voltage          | With 3 mA load<br>With 6 mA load                                                             | 0   |     | 0.4<br>0.8 | V    |

| VOH              | GPIO0-8 output high voltage         | With 6 mA load,<br>VDD>3.0V                                                                  | 2.4 |     | VDD        | V    |

ams Datasheet Page 7

[v1-12] 2018-Feb-26 Document Feedback

| Symbol                 | Parameter                                           | Conditions                                   | Min                  | Тур   | Max  | Unit   |

|------------------------|-----------------------------------------------------|----------------------------------------------|----------------------|-------|------|--------|

| VIH                    | GPIO0-8 input high voltage                          |                                              | 1.25                 |       |      | V      |

| VIL                    | GPIO0-8 input low voltage                           |                                              |                      |       | 0.54 | V      |

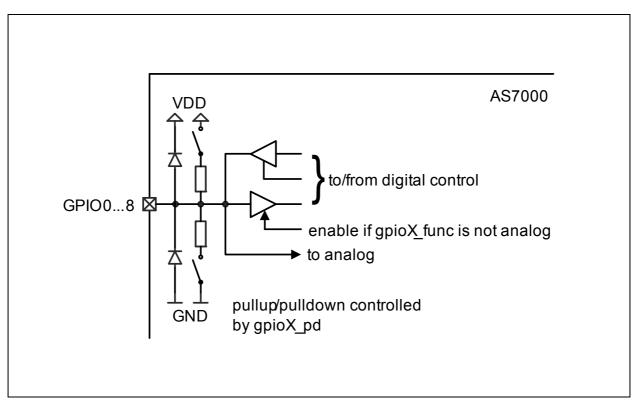

| R <sub>PULLUP</sub>    | Pullup Resistor to VDD                              | On GPIO08 if bit gpioX_<br>pd=1 where X=08   |                      | 75    |      | kΩ     |

| R <sub>PULLDOWN</sub>  | Pulldown Resistor to GND                            | On GPIO08 if bit gpioX_<br>pd=2 where X=08   |                      | 75    |      | kΩ     |

| ILEAK1                 | GPIO0-8                                             |                                              | -1                   |       | 1    | μΑ     |

| ILEAK2                 | VD1-4 pins                                          | At 5.0 V, T <sub>AMB</sub> =25°C             |                      |       | 2    | μΑ     |

| E_f16M                 | Tolerance of internal 16MHz<br>oscillator           | T <sub>AMB</sub> >0°C                        | -2                   |       | +2   | %      |

| E_f3k2                 | Tolerance of internal 512Hz<br>oscillator           |                                              | -35                  |       | +25  | %      |

|                        |                                                     | EEPROM                                       |                      | '     |      |        |

| n <sub>CYCLES</sub>    | Number of write cycles                              |                                              | 100                  |       |      | cycles |

| t <sub>RETENTION</sub> | Data retention time                                 | At maximum 65°C                              |                      |       | 10   | years  |

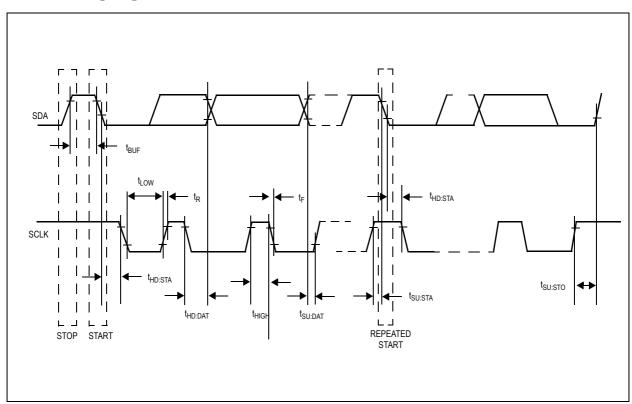

|                        | I <sup>2</sup> C Mode Timings (SCL / SDA Pro        | ogrammable to GPIO Pins –                    | See I <sup>2</sup> C | Mode) |      |        |

| f <sub>SCLK</sub>      | SCL clock frequency                                 |                                              | 0                    |       | 400  |        |

| t <sub>BUF</sub>       | Bus free time between a STOP and START condition    |                                              | 1.3                  |       |      | kHz    |

| t <sub>HD:STA</sub>    | Hold time (repeated) START condition <sup>(3)</sup> |                                              | 0.6                  |       |      | μs     |

| t <sub>LOW</sub>       | LOW period of SCL clock                             |                                              | 1.3                  |       |      | μs     |

| t <sub>HIGH</sub>      | HIGH period of SCL clock                            |                                              | 0.6                  |       |      | μs     |

| t <sub>SU:STA</sub>    | Setup time for a repeated START condition           |                                              | 0.6                  |       |      | μs     |

| t <sub>HD:DAT</sub>    | Data hold time <sup>(4)</sup>                       |                                              | 0                    |       | 0.9  | μs     |

| t <sub>SU:DAT</sub>    | Data Setup Time <sup>(5)</sup>                      |                                              | 100                  |       |      | ns     |

| t <sub>R</sub>         | Rise time of both SDA and SCL signals               |                                              | 20                   |       | 300  | ns     |

| t <sub>F</sub>         | Fall time of both SDA and SCL signals               |                                              | 20                   |       | 300  | ns     |

| t <sub>SU:STO</sub>    | Setup time for STOP condition                       |                                              | 0.6                  |       |      | μs     |

| C <sub>B</sub>         | Capacitive load for each bus Line                   | CB — total capacitance of one bus line in pF |                      |       | 400  | pF     |

Page 8ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

| Symbol           | Parameter                  | Conditions | Min | Тур | Max | Unit |

|------------------|----------------------------|------------|-----|-----|-----|------|

| C <sub>I/O</sub> | I/O capacitance (SDA, SCL) |            |     |     | 10  | pF   |

#### Note(s):

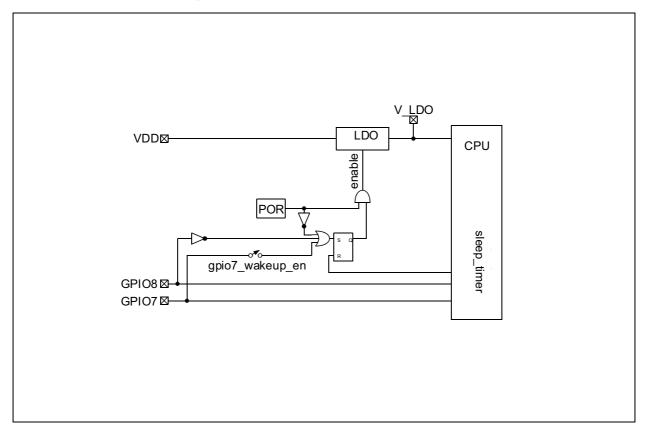

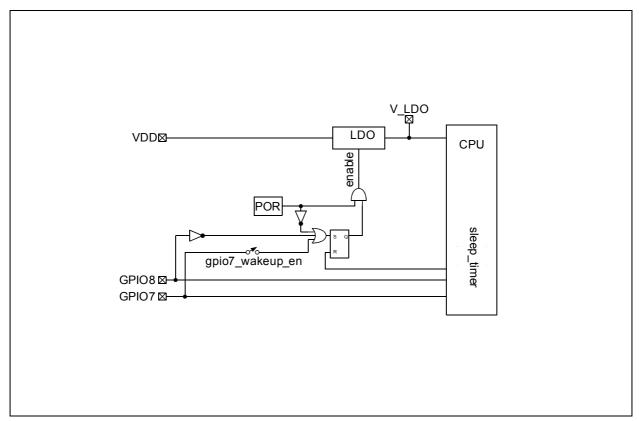

- 1. Deep sleep mode. Use **ams** SDK (software development kit) to enter deep sleep, wakeup with low on GPIO8 pin (if gpio8\_wakeup\_ en=1) or high on GPIO7 (if gpio7\_wakeup\_en=1) or 512Hz oscillator sleep\_timer.

- 2. GPIO0-8 configured to draw minimum current (software dependent).

- 3. Power down mode. Entered by setting enter\_powerdown=1; No oscillator running. Wakeup with low on GPIO8 pin (always) or high on GPIO7 (if gpio7\_wakeup\_en=1).

- 4. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 5. A fast-mode device can be used in a standard-mode system, but the requirement  $t_{SU:DAT} = to 250$ ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_R \max + t_{SU:DAT} = 1000 + 250 = 1250$ ns before the SCL line is released.

Figure 7: I<sup>2</sup>C Mode Timing Diagram

I<sup>2</sup>C Mode Timing Diagram: This figure shows the different timings required for I<sup>2</sup>C communication.

#### Note(s):

1. SCL / SDA Programmable to GPIO Pins – See  $I^2C$  Mode.

ams Datasheet Page 9

[v1-12] 2018-Feb-26 Document Feedback

## **Detailed Description**

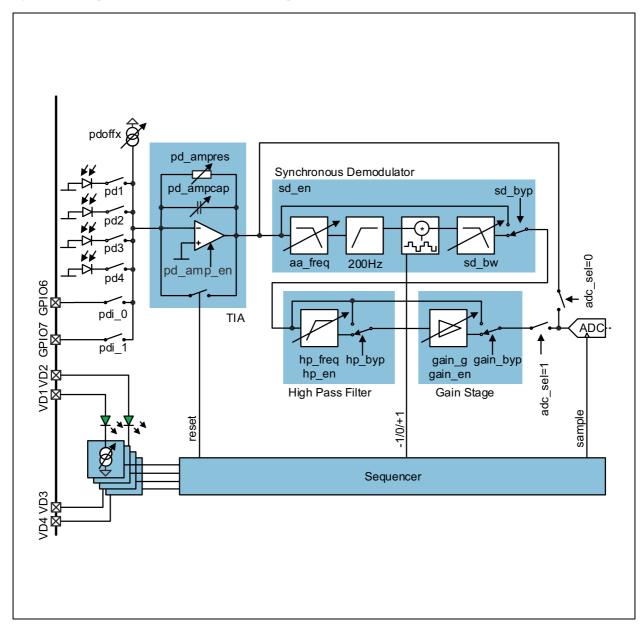

## **Optical Analog Front End**

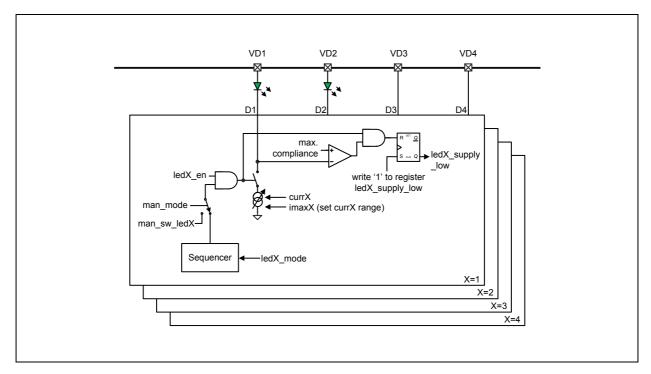

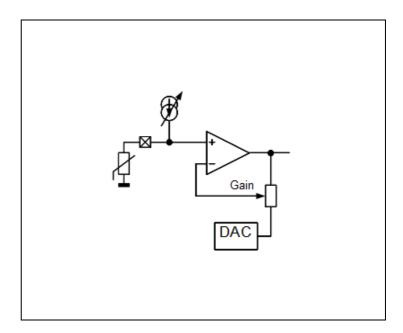

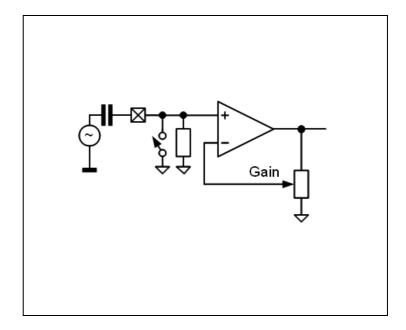

Figure 8:

Optical Analog Front End – AS7000-AA Configuration

#### Note(s):

1. Dual Green LED Configuration is shown.

The number of LEDs inside the module depends on the application – Figure 8 shows 2 LEDs. If a LED is not populated, the current sink is connected directly to the pin (VD3 and VD4 in above figure).

Page 10

Document Feedback

[v1-12] 2018-Feb-26

#### **LEDs**

AS7000-AA Dual Green LED Configuration

Two green LEDs are used (pins VD1/VD2). The other two current sinks are available on pins VD3 and VD4.

**LED Characteristics**

Figure 9: LED Characteristics at T<sub>AMB</sub> =25°C

| Symbol                   | Parameter                                                 | Conditions              | Min | Тур | Max | Unit |

|--------------------------|-----------------------------------------------------------|-------------------------|-----|-----|-----|------|

|                          | Green LI                                                  | ED (AS7000-AA)          |     |     |     |      |

| lung contru              | Allowed operating LED current                             | Continuous              | 0   |     | 50  | mA   |

| <sup>I</sup> LED_GREEN   | range <sup>(1)</sup>                                      | 1/10 duty cycle @ 1 kHz | O   |     | 100 | mA   |

| VF <sub>LED_GREEN</sub>  | Forward voltage (2)                                       | I <sub>LED</sub> =20mA  | 2.9 | 3.2 |     | V    |

| VF <sub>LED+DRIVER</sub> | Voltage on VD1/VD2 where operation of the LED and current | I <sub>LED</sub> = 10mA |     |     | 3.6 | V    |

| _GREEN                   | source is guaranteed                                      | I <sub>LED</sub> = 50mA |     |     | 4.5 |      |

| λp_ <sub>GREEN</sub>     | Dominant wavelength                                       |                         |     | 527 |     | nm   |

| Δλ½ <sub>_GREEN</sub>    | Spectral halfwidth                                        |                         |     | 35  |     | nm   |

#### Note(s):

- 1. The maximum allowed LED current (DC and peak) is specified for 25°C. Lower values apply for higher temperatures.

- 2. Add 280mV and use LED current range  $\leq$ 100mA for designing the VD1/VD2 LED supply (DC-DC converter).

ams Datasheet Page 11

[v1-12] 2018-Feb-26 Document Feedback

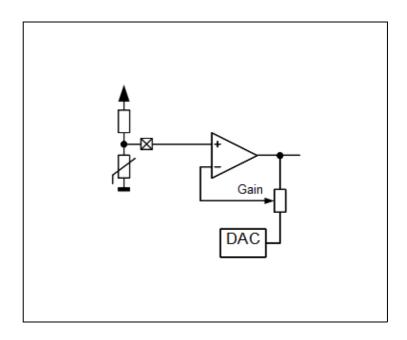

#### **LED-Driver**

The four LED-driver outputs can be controlled manually or by the built in sequencer. See Optical Front End Operating Modes

Figure 10: LED Drivers

#### Note(s):

1. Dual Green LED Configuration.

Figure 11: Operating Characteristics of Each LED Current Sink, VDD=3V, T<sub>AMB</sub>=25°C (unless otherwise noted)

| Symbol                            | Parameter                      | Conditions                                               | Min         | Тур  | Max             | Unit           |

|-----------------------------------|--------------------------------|----------------------------------------------------------|-------------|------|-----------------|----------------|

|                                   | LED output current range       | imax1/2/3/4 = 00<br>imax1/2/3/4 = 01<br>imax1/2/3/4 = 10 | 0<br>0<br>0 |      | 25<br>50<br>100 | mA<br>mA<br>mA |

| I <sub>LED1/2/3/4</sub> Tolerance | 25mA range<br>imax1/2/3/4 = 00 | -5                                                       | -5          |      |                 |                |

|                                   | Tolerance                      | 50mA range<br>imax1/2/3/4 = 01                           | -10         |      | 10              | %              |

|                                   |                                | 100mA range <sup>(1)</sup><br>imax1/2/3/4 = 10           | -10         |      | 10              |                |

| V_Dmin                            | Output voltage compliance      | Voltage compliance of current sinks D1,D2,D3,D4          |             | 0.28 |                 | V              |

| V_Dmax                            | Output voltage maximum         | Pins VD1, VD2, VD3 and VD4                               |             | 5    | 5.5             | V              |

#### Note(s):

1. Not production tested. Only guaranteed by lab characterization.

Page 12ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

## **LED Configuration Registers**

For ledX\_supply\_low registers see register AFE\_PD\_CFG.

Figure 12: AFE\_LED\_CFG

| 0x00: AFE_LED_CFG |                     |                       |     |                                                                                                             |                |  |

|-------------------|---------------------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------|----------------|--|

| Field             | Name                | ame Rst Type Descript |     | iption                                                                                                      |                |  |

| 18                | sigref_en           | 0                     | RW  | Signal reference: Is required for all analog blocks  RW 0Disable signal reference  1Enable signal reference |                |  |

| 11                | led4_en             | 0                     | RW  | 0Disables LED4 output source. 1Enables LED4 output source.                                                  |                |  |

| 10                | led3_en             | 0                     | RW  | 0Disables LED3 output source. 1Enables LED3 output source.                                                  |                |  |

| 9                 | led2_en             | 0                     | RW  | RW 0Disables LED2 output source. 1Enables LED2 output source.                                               |                |  |

| 8                 | led1_en             | 0                     | RW  | 0Disables LED1 output source. 1Enables LED1 output source.                                                  |                |  |

|                   |                     |                       |     | Defines IMAX of LED4.                                                                                       |                |  |

|                   |                     |                       |     | Setting                                                                                                     | IMAX           |  |

| 7:6               | imax4               | 1                     | RW  | 0                                                                                                           | 25mA           |  |

| 7.0               | IIIIdX <del>4</del> | '                     | UAA | 1                                                                                                           | 50mA           |  |

|                   |                     |                       |     | 2                                                                                                           | 100mA          |  |

|                   |                     |                       |     | 3                                                                                                           | Do not use     |  |

| 5:4               | imax3               | 1                     | RW  | Defines IMAX of LED3. same encoding as imax4                                                                |                |  |

| 3:2               | imax2               | 1                     | RW  | Defines IMAX of LED2. same encoding as imax4                                                                |                |  |

| 1:0               | imax1               | 1                     | RW  | Defines IMAX of LED1. same enco                                                                             | oding as imax4 |  |

The LED\_CFG register is used to configure the operating mode of the LED outputs.

ams Datasheet Page 13

[v1-12] 2018-Feb-26 Document Feedback

## AFE\_LED\_CURR Register (Addr: 0x04)

The AFE\_LED\_CURR defines the LED output current.

Figure 13: AFE\_LED\_CURR Register

| Addr: 0x04 |          | AFE_LED_CURR |        |                                                                                                              |  |  |

|------------|----------|--------------|--------|--------------------------------------------------------------------------------------------------------------|--|--|

| Bit        | Bit Name | Default      | Access | Description                                                                                                  |  |  |

| 31:24      | curr4    | 0x00         | R/W    | LED4 output current – do not use code=0 (will generate no output current)  ILED4 = (curr4 + 1) * imax4 / 256 |  |  |

| 23:16      | curr3    | 0x00         | R/W    | LED3 output current – do not use code=0 (will generate no output current)  ILED3 = (curr3 + 1) * imax3 / 256 |  |  |

| 15:8       | curr2    | 0x00         | R/W    | LED2 output current – do not use code=0 (will generate no output current)  ILED2 = (curr2 + 1) * imax2 / 256 |  |  |

| 7:0        | curr1    | 0x00         | R/W    | LED1 output current – do not use code=0 (will generate no output current)  ILED1 = (curr1 + 1) * imax1 / 256 |  |  |

Page 14ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

Figure 14:

AFE\_MAN\_SEQ\_CFG

|       | 0x20: AFE_MAN_SEQ_CFG |     |      |                                                                                                                                           |                                                                                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

|-------|-----------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|

| Field | Name                  | Rst | Type |                                                                                                                                           |                                                                                                                                                  | Descri                                                                                                                                  | ption                                                                                       |                                                                             |                                     |

| 26    | man_mode              | 0   | RW   |                                                                                                                                           | 0Enables Sequencer 1Enables Manual control of optical front end                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

| 23    | man_sw_itg            | 0   | RW   | If man_mode=1 0All integrator capacitors are shorted. Integrator is reset 1Integrator capacitors are charging up. Integrator is running   |                                                                                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

| 22    | man_sw_led4           | 0   | RW   | If man_mode=1 0LED output D4 disabled. (High impedance) 1LED output D4 enabled                                                            |                                                                                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

| 21    | man_sw_led3           | 0   | RW   | If man_mode=1 0LED output D3 disabled. (High impedance) 1LED output D3 enabled                                                            |                                                                                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

| 20    | man_sw_led2           | 0   | RW   | If man_mode=1 0LED output D2 disabled. (High impedance) 1LED output D2 enabled                                                            |                                                                                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

| 19    | man_sw_led1           | 0   | RW   | If man_mode=1 0LED output D1 disabled. (High impedance) 1LED output D1 enabled                                                            |                                                                                                                                                  |                                                                                                                                         |                                                                                             |                                                                             |                                     |

| 18:17 | 18:17 diode_ctrl 0    | 0   | RW   | Connectic<br>photodiod<br>0PD1-PD<br>1PD1 syr<br>sync/to LE<br>2PD1 syr<br>sync/to LE<br>3PD1 syr<br>sync/to LE<br>Note that<br>OFF one p | de amplific<br>04 are conf<br>nchronous<br>D3, PD4 s<br>nchronous<br>D2, PD4 s<br>nchronous<br>D4, PD4 s<br>AFE_PD_C<br>hoto diod<br>erted in th | er. nected to LED1, l ync/to LEE to LED1, l ync/to LEE to LED1, l ync/to LEE crocker to LED1, l ync/to LEE crocker e, the resp e AFE_PD | PD2 sync/<br>PD2 sync/<br>PD2 sync/<br>PD2 sync/<br>okes prece<br>pective bit<br>_CFG regis | to LED2, Pl<br>to LED1, Pl<br>to LED1, Pl<br>dence - to<br>(pd1pd-<br>ster. | D3<br>D3<br>D3<br>turn<br>4) has to |

|       |                       |     |      | AFE_PD_<br>CFG.pdX                                                                                                                        | diode_<br>ctrl                                                                                                                                   | Photo<br>Diode1                                                                                                                         | Photo<br>Diode2                                                                             | Photo<br>Diode3                                                             | Photo<br>Diode4                     |

|       |                       |     |      | 0                                                                                                                                         | xx                                                                                                                                               | OFF                                                                                                                                     | OFF                                                                                         | OFF                                                                         | OFF                                 |

|       |                       |     |      | 1                                                                                                                                         | 00                                                                                                                                               | ON                                                                                                                                      | ON                                                                                          | ON                                                                          | ON                                  |

|       |                       |     |      | 1                                                                                                                                         | 01                                                                                                                                               | LED1                                                                                                                                    | LED2                                                                                        | LED3                                                                        | LED4                                |

|       |                       |     |      | 1                                                                                                                                         | 10<br>11                                                                                                                                         | LED1                                                                                                                                    | LED1<br>LED1                                                                                | LED2<br>LED4                                                                | LED2<br>LED4                        |

|       |                       |     |      | 1                                                                                                                                         | 11                                                                                                                                               | LEUI                                                                                                                                    | LEUI                                                                                        | LED4                                                                        | LEU4                                |

ams Datasheet Page 15

[v1-12] 2018-Feb-26 Document Feedback

|       | 0x20: AFE_MAN_SEQ_CFG |     |      |          |                                                                                                    |  |  |  |  |

|-------|-----------------------|-----|------|----------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Field | Name                  | Rst | Type |          | Description                                                                                        |  |  |  |  |

| 13    | dma_disable           | 0   | RW   | 1ADC re  | ADC DMA disable  1ADC result has to be read from adc_data  0ADC result(s) is/are written to memory |  |  |  |  |

|       |                       |     |      | LED4 mod | de                                                                                                 |  |  |  |  |

|       |                       |     |      | Setting  | Behavior                                                                                           |  |  |  |  |

|       |                       |     |      | 0        | Always OFF                                                                                         |  |  |  |  |

|       |                       |     |      | 1        | Always ON when sequencer is active                                                                 |  |  |  |  |

| 12:10 | led4_mode             | 0   | RW   | 2        | Controlled by sequencer                                                                            |  |  |  |  |

|       |                       |     |      | 3        | Controlled by sequencer, only ON in even iterations: 0, 2, 4 etc.                                  |  |  |  |  |

|       |                       |     |      | 4        | Controlled by sequencer, only ON in odd iterations: 1, 3, 5 etc.                                   |  |  |  |  |

|       |                       |     |      | 5        | Controlled by sequencer, only ON in every fourth iteration, starting at 3: 3, 7, 11 etc.           |  |  |  |  |

|       |                       |     |      | LED3 mod | le                                                                                                 |  |  |  |  |

|       |                       |     |      | Setting  | Behavior                                                                                           |  |  |  |  |

|       |                       |     |      | 0        | Always OFF                                                                                         |  |  |  |  |

|       |                       |     |      | 1        | Always ON when sequencer is active                                                                 |  |  |  |  |

| 9:7   | led3_mode             | 0   | RW   | 2        | Controlled by sequencer                                                                            |  |  |  |  |

|       | .cas_mode             |     |      | 3        | Controlled by sequencer, only ON in even iterations: 0, 2, 4 etc.                                  |  |  |  |  |

|       |                       |     |      | 4        | Controlled by sequencer, only ON in odd iterations: 1, 3, 5 etc.                                   |  |  |  |  |

|       |                       |     |      | 5        | Controlled by sequencer, only on in every fourth iteration, starting at 2: 2, 6, 10 etc.           |  |  |  |  |

Page 16ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

|       | 0x20: AFE_MAN_SEQ_CFG |     |      |                                        |                                                                                         |  |  |  |

|-------|-----------------------|-----|------|----------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Field | Name                  | Rst | Type |                                        | Description                                                                             |  |  |  |

|       |                       |     |      | LED2 mode                              |                                                                                         |  |  |  |

|       |                       |     |      | Setting                                | Behavior                                                                                |  |  |  |

|       |                       |     |      | 0                                      | Always OFF                                                                              |  |  |  |

|       |                       |     |      | 1                                      | Always ON when sequencer is active                                                      |  |  |  |

| 6:4   | led2_mode             | 0   | RW   | 2                                      | Controlled by sequencer                                                                 |  |  |  |

|       |                       |     |      | 3                                      | Controlled by sequencer, only ON in even iterations: 0, 2, 4 etc.                       |  |  |  |

|       |                       |     |      | 4                                      | Controlled by sequencer, only ON in odd iterations: 1, 3, 5 etc.                        |  |  |  |

|       |                       |     |      | 5                                      | Controlled by sequencer, only ON in every fourth iteration, starting at 1: 1, 5, 9 etc. |  |  |  |

|       |                       |     |      | LED1 mode                              |                                                                                         |  |  |  |

|       |                       |     |      | Setting                                | Behavior                                                                                |  |  |  |

|       |                       |     |      | 0                                      | Always OFF                                                                              |  |  |  |

|       |                       |     |      | 1                                      | Always ON when sequencer is active                                                      |  |  |  |

| 3:1   | led1_mode             | 0   | RW   | 2                                      | Controlled by sequencer                                                                 |  |  |  |

|       |                       |     |      | 3                                      | Controlled by sequencer, only ON in even iterations: 0, 2, 4 etc.                       |  |  |  |

|       |                       |     |      | 4                                      | Controlled by sequencer, only ON in odd iterations: 1, 3, 5 etc.                        |  |  |  |

|       |                       |     |      | 5                                      | Controlled by sequencer, only ON in every fourth iteration, starting at 0: 0, 4, 8 etc. |  |  |  |

| 0     | seq_en                | 0   | RW   | 0Disables sequencer 1Enables sequencer |                                                                                         |  |  |  |

ams Datasheet Page 17

[v1-12] 2018-Feb-26 Document Feedback

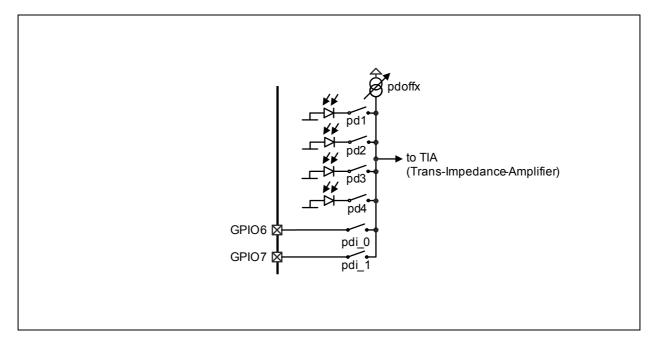

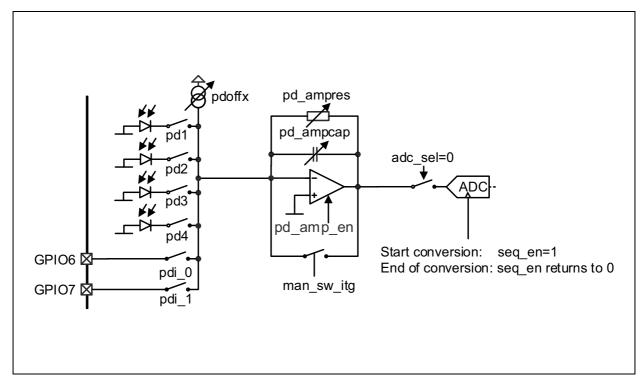

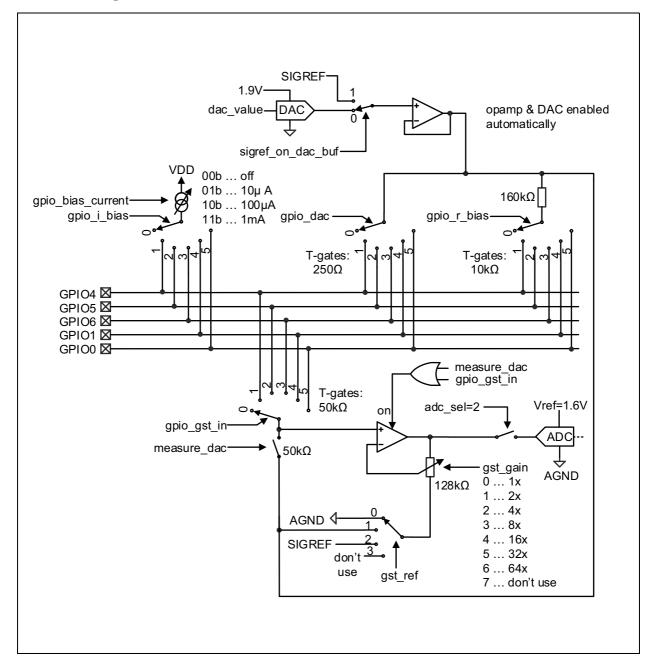

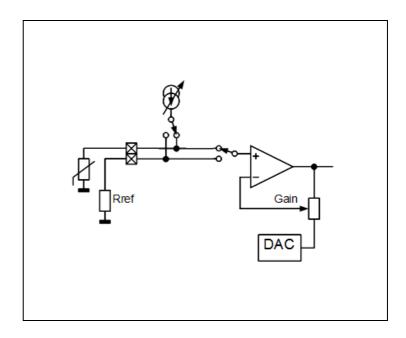

#### **Photodiode Selection**

In order to have flexible arrangement of the use photodiodes, PD1-PD4 can be individually connected to the photodiode amplifier input. The optional offset current allows cancellation of constant light sources like sunlight. In case of an external photodiode or any other sensor with (low) current output, the pins GPIO6 and GPIO7 can be used as input.

Additionally the sequencer can control the diodes – see diode\_ctrl described in register AFE\_MAN\_SEQ\_CFG .

Figure 15: Photodiode Selection

Page 18

Document Feedback

[v1-12] 2018-Feb-26

AFE\_PD\_CFG Register (Addr: 0x08)

The AFE\_PD\_CFG register is used to configure the input to the photo amplifier.

Figure 16: AFE\_PD\_CFG Register

| Addr: 0x08 |                     |         |                      | AFE_PD_CFG                                                                                                                                                    |

|------------|---------------------|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name            | Default | Access               | Description                                                                                                                                                   |

| 25         | sd_hld              | 0       | R/W                  | SD hold 0Output of synchronous demodulator is forced to SIGREF if not set to +1 or -1 1 Output of synchronous demodulator is tristated if not set to +1 or -1 |

| 23         | led4_<br>supply_low | 0       | SC_WS <sup>(1)</sup> | If this bit is cleared, LED4 current sink voltage was below its compliance voltage                                                                            |

| 22         | led3_<br>supply_low | 0       | SC_WS (1)            | If this bit is cleared, LED3 current sink voltage was below its compliance voltage.                                                                           |

| 21         | led2_<br>supply_low | 0       | SC_WS <sup>(1)</sup> | If this bit is cleared, LED2 current sink voltage was below its compliance voltage.                                                                           |

| 20         | led1_<br>supply_low | 0       | SC_WS <sup>(1)</sup> | If this bit is cleared, LED1 current sink voltage was below its compliance voltage.                                                                           |

| 15:8       | pdoffx              | 0x00    | R/W                  | Input offset current Ioffset = pdoffx*10nA 0000000Offset source is turned OFF                                                                                 |

| 5          | pd4                 | 0       | R/W                  | 0Photodiode PD4 is disconnected from photo amplifier 1Photodiode PD4 is connected to photo amplifier (as defined in diode_ctrl)                               |

| 4          | pd3                 | 0       | R/W                  | 0Photodiode PD3 is disconnected from photo amplifier<br>1Photodiode PD3 is connected to photo amplifier (as<br>defined in diode_ctrl)                         |

| 3          | pd2                 | 0       | R/W                  | 0Photodiode PD2 is disconnected from photo amplifier<br>1Photodiode PD2 is connected to photo amplifier (as<br>defined in diode_ctrl)                         |

| 2          | pd1                 | 0       | R/W                  | 0Photodiode PD1 is disconnected from photo amplifier 1Photodiode PD1 is connected to photo amplifier (as defined in diode_ctrl)                               |

| 1          | pdi_1               | 0       | R/W                  | 0GPIO7-input is disconnected from photo amplifier 1GPIO7-input is connected to photo amplifier                                                                |

| 0          | pdi_0               | 0       | R/W                  | 0GPIO6-input is disconnected from photo amplifier 1GPIO6-input is connected to photo amplifier                                                                |

#### Note(s):

1. SC\_WS: Self clear, write sets: These registers are reset by the hardware. Set to '1' before using them.

ams Datasheet Page 19

[v1-12] 2018-Feb-26 Document Feedback

#### **Photodiode Characteristics**

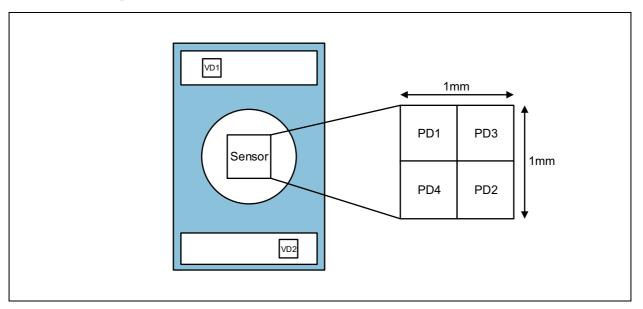

Figure 17: Photodiode Arrangement

#### Note(s)

1. Orientation as in Figure 115 or Figure 3.

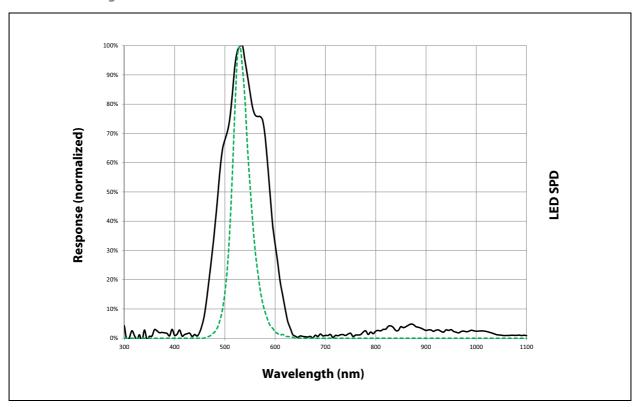

Figure 18:

AS7000-AA Photodiode Sensitivity (Solid Black) and LED Emission Spectrum (Dotted Green) – Dual Green LED Configuration

#### Note(s):

- 1. Perpendicular light source.

- 2. LEDs and Filters are shown for Dual Green LED Configuration.

Page 20ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

Figure 19: Operating Characteristics of Each Photodiode, VDD=3V, T<sub>AMB</sub>=25°C (unless otherwise noted)

| Symbol | Parameter                   | Conditions                                                                                                                                      | Min | Тур | Max | Unit                             |

|--------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----------------------------------|

| Re     | Irradiance<br>responsivity  | $\lambda_{p}$ =525nm,<br>4 photodiodes used pd1/2/3/4=1,<br>gain_g=4x, gain_en=1, pd_ampres=7M $\Omega$<br>dual green LED configuration filters |     | 76  |     | mV/<br>(μW<br>/cm <sup>2</sup> ) |

| Id     | Dark current                | E <sub>e</sub> =0                                                                                                                               | 0   |     | 1   | nA                               |

| los    | Extrapolated offset current |                                                                                                                                                 | -1  |     | 1   | nA                               |

#### Note(s):

ams Datasheet Page 21

[v1-12] 2018-Feb-26 Document Feedback

<sup>1.</sup> For monochromatic light of 555nm, one lux corresponds to 0.146  $\mu$ W/cm2. That is, one obtains 6.5 lux per  $\mu$ W/cm2

## Photodiode Trans-Impedance Amplifier (TIA)

The photodiode amplifier can be configured in three different modes:

- Photocurrent to frequency converter

- Photocurrent to voltage converter

- Photocurrent integrator

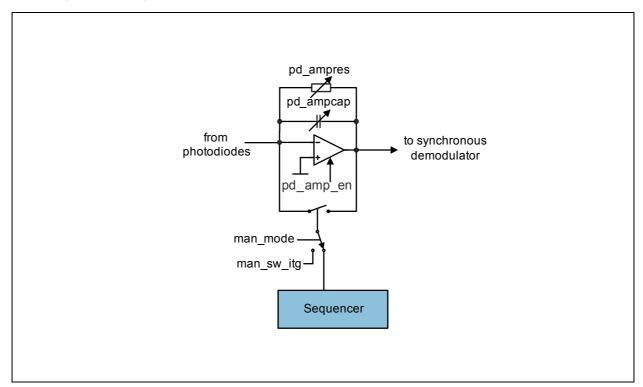

Figure 20: Trans-Impedance-Amplifier (TIA)

The integration time  $t_{INT}$  is defined either by the sequencer (man\_mode=0) of manually through the bit sw\_itg if man\_mode=1.

Page 22ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

Figure 21: Settings for the Programming of the TIA

| pd_ampres                      | pd12341 | pd_ampcap | pd_ampcomp | pd_ampvo | Gain       |  |  |  |

|--------------------------------|---------|-----------|------------|----------|------------|--|--|--|

| 1                              | 14      | 13        | 1          | 15       | 1V/μΑ      |  |  |  |

| 2                              | 14      | 7         | 1          | 15       | 2V/μA      |  |  |  |

| 3                              | 14      | 5         | 1          | 15       | 3V/μA      |  |  |  |

| 4                              | 12      | 2         | 0          | 15       | 5V/μA      |  |  |  |

| 7                              | 34      | 3         |            | 13       | 3ν/μΛ      |  |  |  |

| 5                              | 12      | 2         | 0          | 15       | 7V/μΑ      |  |  |  |

| ,                              | 34      | 3         |            | 13       |            |  |  |  |

| 6                              | 1       | 1         | 0          | 15       | 10V/μA     |  |  |  |

|                                | 24      | 2         |            | 13       | 10 τ/ μ/ τ |  |  |  |

| 7                              | 12      | 1         | 0          | 15       | 15V/μA     |  |  |  |

| ,                              | 34      | 2         |            | 15       | 13ν/μΑ     |  |  |  |

|                                |         | Low Bandy | vidth Mode |          |            |  |  |  |

| 5                              | 14      | 31        | 3          | 15       | 7V/μA      |  |  |  |

| Integrating Mode (pd_ampres=0) |         |           |            |          |            |  |  |  |

| 0                              | 14      | 10        | 3          | 15       | 1V/pQ      |  |  |  |

| 0                              | 14      | 20        | 3          | 15       | 1/2V/pQ    |  |  |  |

| 0                              | 14      | 30        | 3          | 15       | 1/3V/pQ    |  |  |  |

#### Note(s):

$1.\ pd1234\ ...\ number\ of\ active\ photodiodes\ (for\ example,\ pd1=1,\ pd2=0,\ pd3=1,\ pd4=0\ ->\ pd1234=2)$

ams Datasheet Page 23

[v1-12] 2018-Feb-26 Document Feedback

AFE\_PD\_AMPCFG Register (Addr: 0x0c)

The AFE\_PD\_AMPCFG register is used to configure the operating mode of the photo-amplifier

Figure 22: AFE\_PD\_AMPCFG Register

| Addr: 0x0c |                | AFE_PD_AMPCFG |        |                                                                                                                                      |  |

|------------|----------------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name       | Default       | Access | Description                                                                                                                          |  |

| 31         | pd_amp_en      | 0             | R/W    | 0Activates power down mode of photo-amplifier 1Enables photo-amplifier                                                               |  |

| 13:10      | pd_amp_vo      | 15            | R/W    | Opamp offset. Use <b>ams</b> device drivers – these automatically configure this register.                                           |  |

| 9:8        | pd_<br>ampcomp | 3             | R/W    | Opamp compensation. Use <b>ams</b> device drivers – these automatically configure this register.                                     |  |

| 7:5        | pd_ampres      | 0x0           | R/W    | Feedback resistor 000No resistor in feedback of amplifier 0011MΩ 0102MΩ 0113MΩ 1005MΩ 1017MΩ 11115MΩ                                 |  |

| 4:0        | pd_ampcap      | 0x0           | R/W    | Feedback capacitor – automatically set by <b>ams</b> device drivers for modes using pd_ampres not 000b.  Capacitor = pd_ampcap*0.1pF |  |

For registers man\_mode and man\_sw\_itg see AFE\_MAN\_SEQ\_CFG .

Page 24ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

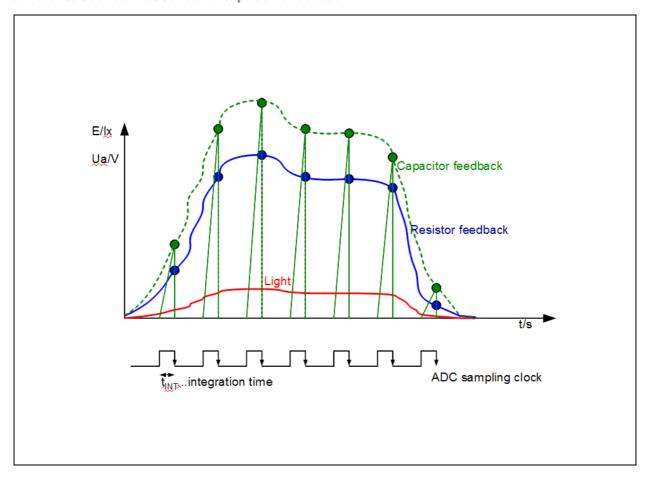

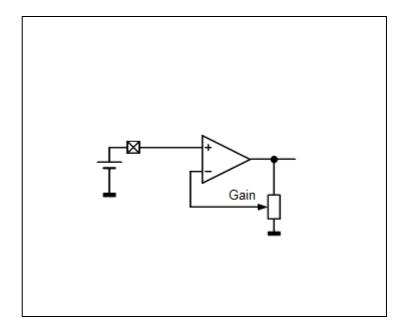

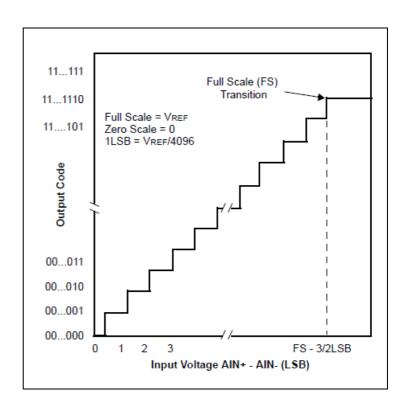

## Voltage Mode of the Photodiode Amplifier

The output voltage of the photodiode amplifier is depending on the feedback component:

(EQ1) Feedback resistor:  $U_{out} = I_{photo} \cdot R_{fb}$

(EQ2) Feedback capacitor:

$$U_{out} = I_{photo} \cdot \frac{t_{INT}}{C_{fb}}$$

**Note(s):** The integration time  $t_{INT}$  is defined either by the sequencer (man\_mode=0) of manually through the bit sw\_itg if man\_mode=1.

For the synchronous demodulator only use the resistive feedback.

Figure 23:

Difference Between Resistive and Capacitive Feedback

ams Datasheet Page 25

[v1-12] 2018-Feb-26 Document Feedback

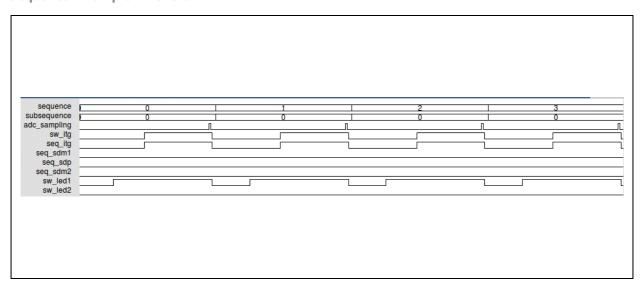

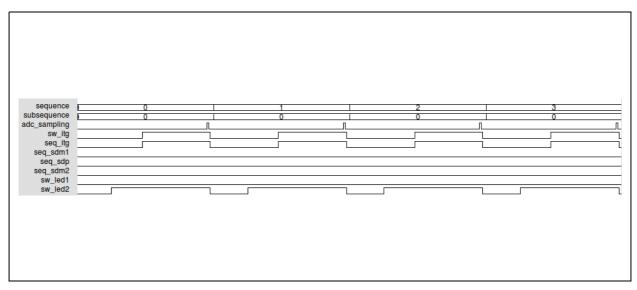

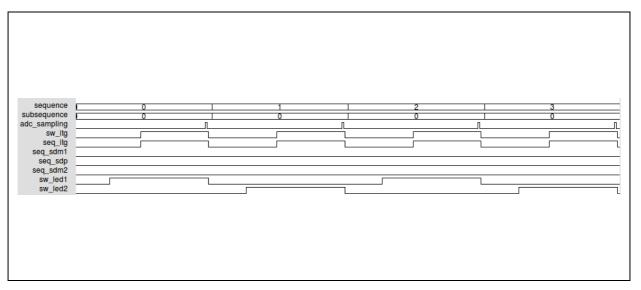

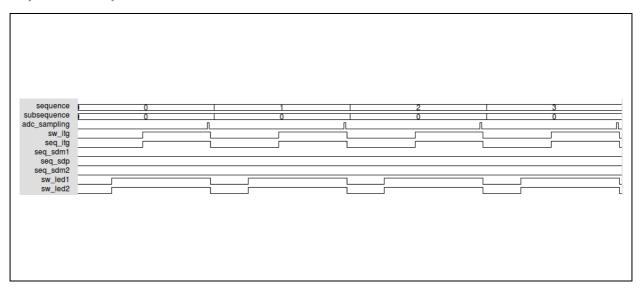

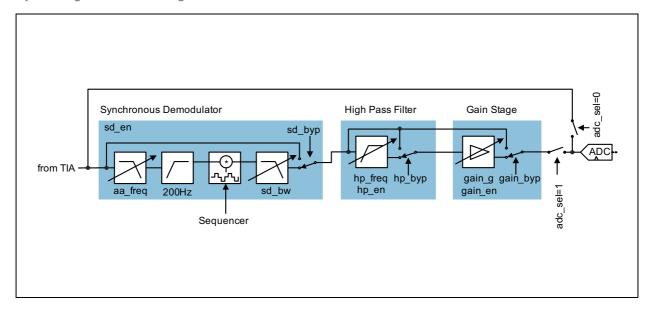

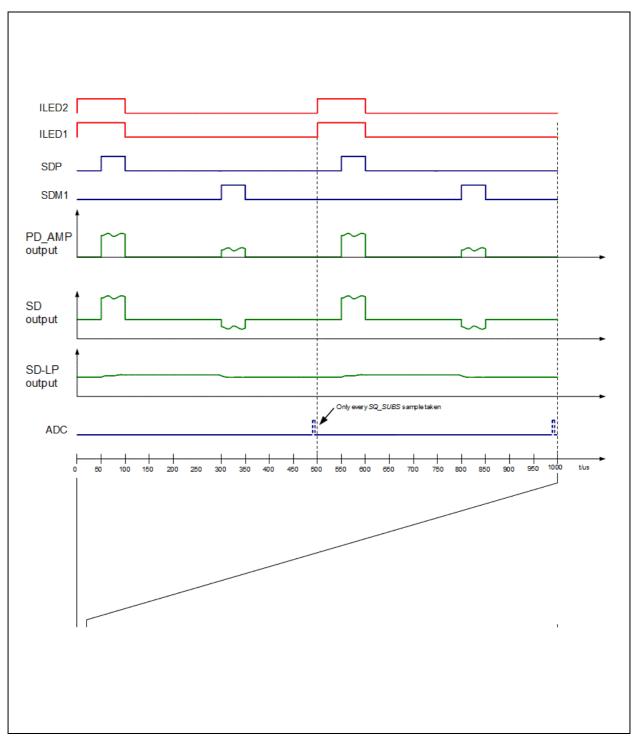

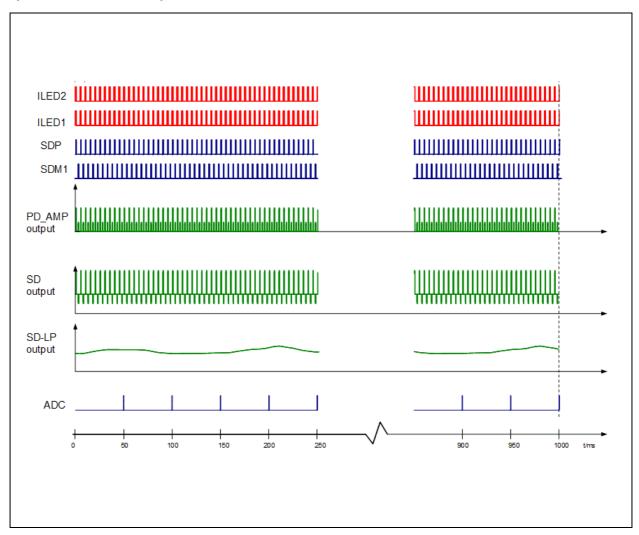

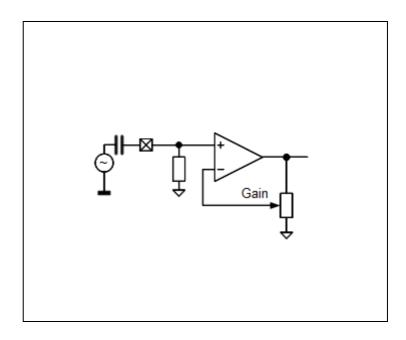

## **Optical Front End Operating Modes**

Once the photodiode amplifier is configured the measurement can be done in two different ways. Either the LED-outputs, the photodiode amplifier and the ADC are controlled manually by means of register bits, or they are controlled by a built in sequencer.

#### Manual Operation of The Optical Frontend:

The optical front end can be manually controlled via the AFE\_MAN\_SEQ\_CFG register using man\_mode=1.

Figure 24:

Manual Operation of the Optical Frontend and LED

#### Note(s):

1. Applies only if man\_mode=1.

For manual operation of the LEDs and its current sinks see LED-Driver.

Page 26

Document Feedback

[v1-12] 2018-Feb-26

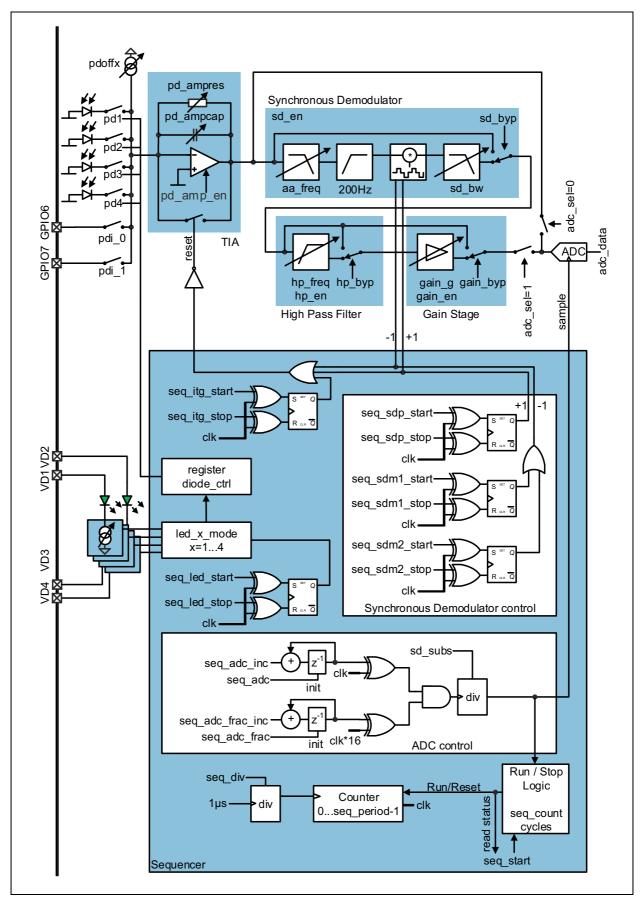

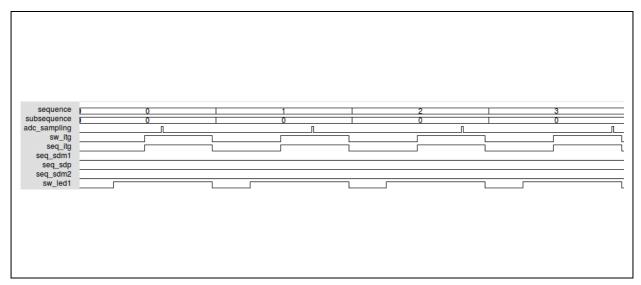

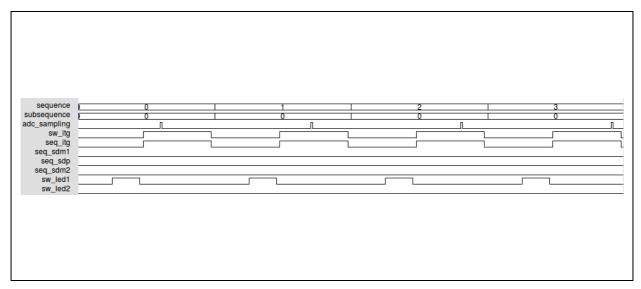

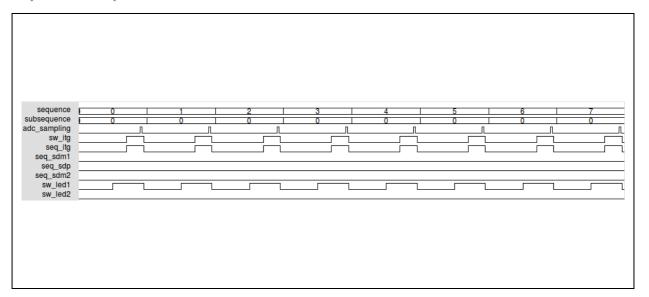

## Sequencer

In order to synchronize the LED-currents, the integration time and the ADC-sampling time, a built in sampling Sequencers can be used. The sequencer generates the 16 bit-timings based on a 1µs clock. The results of the analog to digital conversion are automatically stored in a pipeline buffer or in register adc\_data.

The timings can be programmed with following registers (apply for man\_mode=0):

Figure 25: Sequencer Control Registers Overview

| Register                       | Description                                                                                                                                                                 |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| seq_div                        | Divider of the 1µs input clock                                                                                                                                              |

| seq_count                      | Number of measurements in one sequence                                                                                                                                      |

| seq_start                      | Writing 1 starts the sequencer, 0 stops the sequencer                                                                                                                       |

| seq_period                     | Time of one measurement cycle                                                                                                                                               |

| seq_led_start                  | Start time of the LED drivers within one cycle                                                                                                                              |

| seq_led_stop                   | Stop time of the LED drivers within one cycle                                                                                                                               |

| seq_itg_start                  | Start time of the integrator                                                                                                                                                |

| seq_itg_stop                   | Stop time of the integrator                                                                                                                                                 |

| seq_sdp_start                  | Start time of the synchronous demodulator's positive multiplication                                                                                                         |

| seq_sdp_stop                   | Stop time of the synchronous demodulator's positive multiplication                                                                                                          |

| seq_sdm1_start                 | Start time of the synchronous demodulator's negative multiplication 1                                                                                                       |

| seq_sdm1_stop                  | Stop time of the synchronous demodulator's negative multiplication 1                                                                                                        |

| seq_sdm2_start                 | Start time of the synchronous demodulator's negative multiplication 2                                                                                                       |

| seq_sdm2_stop                  | Stop time of the synchronous demodulator's negative multiplication 2                                                                                                        |

| seq_adc, seq_adc_fract         | Sampling position of the ADC in single steps / in 1/16th steps                                                                                                              |

| seq_adc_inc, seq_adc_inc_fract | Increment of the sampling position of the ADC after each measurement in single steps / in 1/16th steps                                                                      |

| sd_subs                        | Subsampling ratio between sequencer frequency and ADC sampling frequency – use for adjusting the ADC sampling frequency at a lower speed than the sequencer cycle frequency |

#### Note(s):

1. The lowest data value of all registers except seq\_count, seq\_div, seq\_adc\_inc, seq\_adc\_inc\_fract and seq\_adc\_fract is 1.

ams Datasheet Page 27

[v1-12] 2018-Feb-26 Document Feedback

Figure 26: Block Diagram of Sequencer

Page 28ams DatasheetDocument Feedback[v1-12] 2018-Feb-26

## Sequencer Registers

For registers man\_mode, man\_sw\_sdmult, man\_sw\_sdpol, man\_sw\_itg, man\_sw\_led4, man\_sw\_led3, man\_sw\_led2, man\_sw\_led1, diode\_ctrl, dma\_disable, led4\_mode, led3\_mode, led2\_mode and led1\_mode, seq\_en see AFE\_MAN\_SEQ\_CFG .

For register sd\_subs see AFE\_SC\_CFG .

AFE\_SEQ\_DIV\_CNT Register (Addr: 0x24)

The AFE\_SEQ\_DIV\_CNT register sets the input divider for the main clock.

Figure 27:

AFE\_SEQ\_DIV\_CNT Register

| Addr: 0x24 |           | AFE_SEQ_DIV_CNT |        |                                                                                                    |  |

|------------|-----------|-----------------|--------|----------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name  | Default         | Access | Description                                                                                        |  |

| 23:8       | seq_div   | 0x0000          | R/W    | Divider value; Sequencer time increment $t_{clk} = (seq\_div + 1) * 1\mu s$                        |  |

| 7:0        | seq_count | 0x00            | R/W    | Number of measurements in one sequence. IF seq_count = 0x00 the sequencer is running continuously. |  |

AFE\_SEQ\_START Register (Addr: 0x28)

In AFE\_SEQ\_START register the configured sequencer can be started.

Figure 28: AFE\_SEQ\_START Register

| Addr: 0x28 |           | AFE_SEQ_START |        |                                                                                                                                                                                                                                                                                                                                                                                |  |

|------------|-----------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name  | Default       | Access | Description                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0          | seq_start | 0             | R/W    | 1Starts the sequencer. Sequencer is running according to the configurations in the sequencer registers Writing 0 stops the sequencer(s). In manual mode, writing 1 starts one ADC conversion. Reading returns 1 if the sequencer is running (sequencer mode), respectively if the ADC is converting (manual mode) and it returns to 0 once the ADC has finished its conversion |  |

ams Datasheet Page 29

[v1-12] 2018-Feb-26 Document Feedback

AFE\_SEQ\_PER Register (Addr: 0x2C)

The AFE\_SEQ\_PER register sets one measurement cycle of the sequencer.

Figure 29: AFE\_SEQ\_PER Register

| Addr: 0x2C |            | AFE_SEQ_PER |        |                                                     |  |

|------------|------------|-------------|--------|-----------------------------------------------------|--|

| Bit        | Bit Name   | Default     | Access | Description                                         |  |

| 15:0       | seq_period | 0x0000      | R/W    | Sequencer period  T = seq_period * seq_div * 1\mu s |  |

AFE\_SEQ\_LED Register (Addr: 0x30)

The AFE\_SEQ\_LED register sets the LED drive timing. Data is stored as 16-bit value

Figure 30: AFE\_SEQ\_LED Register

| Addr: 0x30 |               | AFE_SEQ_LED |        |                                                                                                                     |  |

|------------|---------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name      | Default     | Access | Description                                                                                                         |  |

| 31:16      | seq_led_start | 0x0000      | R/W    | LED start time; the LED starts one cycle later to allow the analog biasing to settle before the current is enabled. |  |

| 15:0       | seq_led_stop  | 0x0000      | R/W    | LED stop time                                                                                                       |  |

AFE\_SEQ\_ITG Register (Addr: 0x34)

The AFE\_SEQ\_ITG register sets the photoamplifier integration time if using capacitive feedback respectively removes the short of the resistive feedback. Data is stored as 16-bit value

Figure 31: AFE\_SEQ\_ITG Register

| Ad    | dr: 0x34      | AFE_SEQ_ITG |        |                                                                                                                                                                                                                                       |  |  |  |

|-------|---------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit   | Bit Name      | Default     | Access | Description                                                                                                                                                                                                                           |  |  |  |

| 31:16 | seq_itg_start | 0x0001      | R/W    | Integrator start time (start time=1 and stop time=0 means that it's - by default - always ON) Turning OFF the integrator actually means discharge the capacitor for capacitive integration mode, without the synchronous demodulator. |  |  |  |

| 15:0  | seq_itg_stop  | 0x0000      | R/W    | Integrator stop time                                                                                                                                                                                                                  |  |  |  |

Page 30

Document Feedback

[v1-12] 2018-Feb-26

#### AFE\_SEQ\_SDP Register (Addr: 0x38)

The AFE\_SEQ\_SDP register sets the synchronous demodulator positive multiplication time. Data is stored as 16-bit value

Figure 32: AFE\_SEQ\_SDP Register

| Ac    | ldr: 0x38     |         | AFE_SEQ_SDP |                                    |  |  |  |  |

|-------|---------------|---------|-------------|------------------------------------|--|--|--|--|

| Bit   | Bit Name      | Default | Access      | Description                        |  |  |  |  |

| 31:16 | seq_sdp_start | 0x0000  | R/W         | Positive multiplication start time |  |  |  |  |

| 15:0  | seq_sdp_stop  | 0x0000  | R/W         | Positive multiplication stop time  |  |  |  |  |

AFE\_SEQ\_SDM1 Register (Addr: 0x3C)

The AFE\_SEQ\_SDM1 register sets the synchronous demodulator negative multiplication time 1. Data is stored as 16-bit value

Figure 33: AFE\_SEQ\_SDM1 Register

| Ad    | ldr: 0x3C      | AFE_SEQ_SDM1 |        |                                      |  |  |  |

|-------|----------------|--------------|--------|--------------------------------------|--|--|--|

| Bit   | Bit Name       | Default      | Access | Description                          |  |  |  |

| 31:16 | seq_sdm1_start | 0x0000       | R/W    | Negative multiplication start time 1 |  |  |  |

| 15:0  | seq_sdm1_stop  | 0x0000       | R/W    | Negative multiplication stop time 1  |  |  |  |

AFE\_SEQ\_SDM2 Register (Addr: 0x40)

The AFE\_SEQ\_SDM2 register sets the synchronous demodulator negative multiplication time 2. Data is stored as 16-bit value

Figure 34: AFE\_SEQ\_SDM2 Register

| Ac    | ldr: 0x40      | AFE_SEQ_SDM2 |        |                                      |  |  |  |

|-------|----------------|--------------|--------|--------------------------------------|--|--|--|

| Bit   | Bit Name       | Default      | Access | Description                          |  |  |  |

| 31:16 | seq_sdm2_start | 0x0000       | R/W    | Negative multiplication start time 2 |  |  |  |

| 15:0  | seq_sdm2_stop  | 0x0000 R/W   |        | Negative multiplication stop time 2  |  |  |  |

ams Datasheet Page 31

[v1-12] 2018-Feb-26 Document Feedback

#### AFE\_SEQ\_ADC Register (Addr: 0x44)

The AFE\_SEQ\_ADC register defines the time when the ADC starts sampling during each measurement cycle. The fraction setting permits a definition of the sampling point as a 1/16 fraction of a sequencer cycle. If seq\_div=0 (1us sequencer clock), then one unit is equivalent to 62.5ns. If, e.g. seq\_div=4 (5us) then the resolution of the fract register is 62.5ns\*5=312.5ns

Figure 35: AFE\_SEQ\_ADC Register

|       | Addr: 0x44        | AFE_SEQ_ADC |        |                                                                                                            |  |  |  |

|-------|-------------------|-------------|--------|------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit   | Bit Name          | Default     | Access | Description                                                                                                |  |  |  |

| 31:28 | seq_adc_inc_fract | 0x0         | R/W    | ADC delay increment : seq_adc_inc_fract/16 fractional                                                      |  |  |  |

| 27:24 | seq_adc_fract     | 0x0         | R/W    | ADC start delay:<br>seq_adc_fract/16 fractional                                                            |  |  |  |

| 23:16 | seq_adc_inc       | 0x00        | R/W    | ADC increment to the adc sample time after each conversion.                                                |  |  |  |

| 15:0  | seq_adc           | 0x0000      | R/W    | ADC Sampling time; changes of this register have no effect as long as the sequencer is running (seq_en=1). |  |  |  |

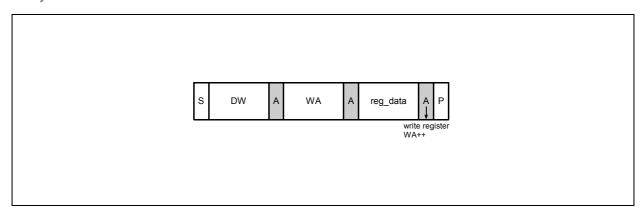

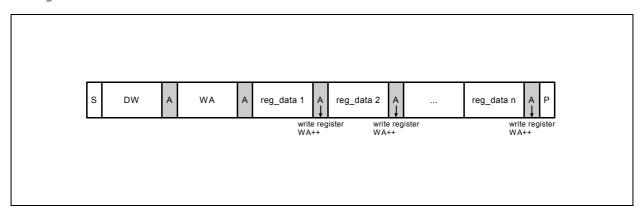

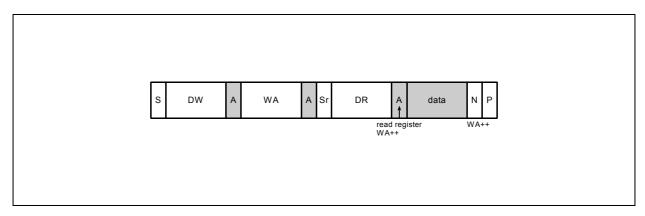

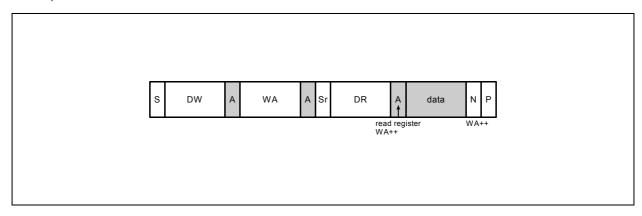

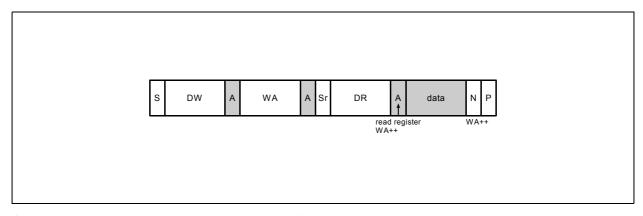

#### AFE\_SEQ\_COUNTER Register (Addr: 0x80)